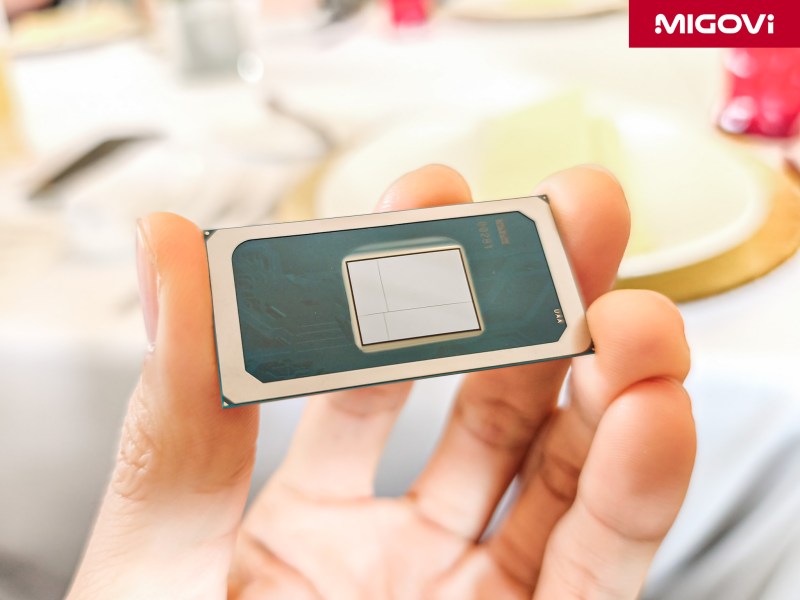

CoPoS - Công nghệ làm chip 'khổng lồ' tiếp theo của TSMC

Khi transistor không nhỏ được nữa thì chip cứ bự ra thôi.

Nếu công nghệ CoW/SoW mà chúng ta từng tìm hiểu còn chưa làm bạn hết "bàng hoàng", thì mới đây, CoPoS có thể sẽ là thuật ngữ mới đẩy sự "bàng hoàng" của bạn lên một tầm cao mới. Theo thông tin từ Nhật báo Kinh tế Đài Loan (UDN), TSMC đang xây một dây chuyền sản xuất thử nghiệm CoPoS tại khu phức hợp Gia Nghĩa (Đài Loan). Và nếu mọi thứ thuận lợi, việc sản xuất hàng loạt sẽ có thể xảy ra trong 2029 tới.

CoPoS (chip-on-panel-on-substrate) hay CoP, cũng có ý nghĩa tương tự CoWoS (chip-on-wafer-on-subtrate) hay CoW, với việc con chip (tổng) được tạo ra từ nhiều chiplet để liên kết với nhau thông qua một tấm nền chung. Khác biệt ở đây là thay vì tấm nền được đặt trên tấm wafer hình tròn thì nó sẽ nằm trên tấm panel dạng vuông/chữ nhật. Còn nhớ mới 1 năm trước, đã có tin đồn TSMC sẽ dùng wafer dạng chữ nhật để sản xuất chip. Với thông tin mới này, dường như điều trên đang ngày một thực tế hơn.

Một nguyên nhân chính cho việc chuyển từ CoW sang CoP chính là nếu kích thước die chip càng lớn, thì phần diện tích bị bỏ đi trên tấm wafer tròn sẽ càng nhiều. Và trên các tiến trình mới nhất, chi phí đang ngày một đắt đỏ hơn. Nên phần diện tích thừa bỏ đi càng cao đồng nghĩa với chi phí của từng die chip càng cao gấp bội. Do vậy, tấm panel hình vuông/chữ nhật sẽ có tính kinh tế cao hơn nếu kích thước chip ngày càng to hơn. Dĩ nhiên, không thể bỏ qua yếu tố làm sao để sản xuất tấm panel dạng vuông vì nó sẽ khác nhiều tấm wafer tròn. Trước mắt, nguồn tin cho hay dây chuyền CoPoS của TSMC sẽ làm ra tấm panel có kích thước 310 x 310 mm, tức nhỉnh hơn đường kính tấm wafer 300 mm một ít.

Cũng theo nguồn trên, NVIDIA có thể là khách hàng đầu tiên sử dụng CoPoS, khi họ là hãng đang làm ra những GPU lớn nhất thế giới. AMD và Broadcom cũng có thể là khách hàng tiềm năng cho công nghệ này, dù trước mắt 2 giải pháp CoWoS-R và CoWoS-L tương đối phù hợp hơn.