Công nghệ làm chip TSMC CoW-SoW và sự 'điên loạn' của ngành bán dẫn

Thời kỳ những con chip to bằng móng tay, ngón tay, bàn tay... sắp hết. Tới đây bạn sẽ thấy "con chip" to bằng cái nồi cơm, bếp điện... và ai biết liệu có bằng cả cái bàn hay không?

Nội dung bài viết

Nhắc lại chút lịch sử

Khoảng gần một thế kỷ trước, khi mà ngành bán dẫn còn chưa thành hình, từ "chip" được hiểu là những thứ nhỏ nhắn, vụn vặt, thường là đồ ăn vụn (a bag of chips). Trong một số trò chơi như poker thì "chip" đại diện cho một số tiền, tất nhiên, là kiểu dáng nhỏ gọn thôi (cỡ như mảnh khoai tây chiên trong các hộp/bịch snack ăn vặt). Vì thế khi mà "chip" điện tử (IC) ra đời vào những thập niên 60, từ này còn ám chỉ đó là những vi mạch có kích thước nhỏ gọn (microchip), bự không quá lòng bàn tay...

"Chip" được hiểu là vật thể nhỏ bé

Dĩ nhiên khái niệm trên vẫn đúng cho tới ít nhất là hôm nay, một phần nhờ vào định luật Moore - khi mà kích thước transistor cứ thu nhỏ dần đi theo năm tháng. Nhưng định luật Moore không phải là định luật vật lý. Nói cho đúng - nó là một xu thế của ngành bán dẫn. Và xu thế này dĩ nhiên không thể nào vượt qua được các quy tắc vật lý nghèo ngặt nhất, nhất là quy tắc lượng tử. Nếu những con chip của thế kỷ có các chi tiết vi mạch (feature) dày từ vài tỷ tới vài triệu nguyên tử, thì giờ đây chúng chỉ còn vài ngàn tới vài trăm (sắp tới là vài chục). Khi bề dày các chi tiết không còn đủ để cách điện thì hiện tượng chui hầm lượng tử (quantum tunnelling) xảy ra và bản chất ON/OFF tuỳ ý của transistor bị phá vỡ - con chip trở nên vô dụng.

Hiện tượng hầm lượng tử làm hỏng mục đích làm ra transistor

Song một chi tiết mà nhiều người bỏ qua khi nhắc tới định luật Moore là mục đích sau cùng của việc thu nhỏ transistor. Tại sao chúng ta cần phải thu nhỏ chúng?

Thực tế trần trụi - con chip mạnh hơn khi có nhiều transistor hơn. Tuy kiến trúc chip có ảnh hưởng không nhỏ tới hiệu năng song một xu thế không thể phủ nhận là hầu như các thế hệ chip sau đều có nhiều transistor hơn thế hệ trước. Định luật Moore chỉ có ý nghĩa khi chúng ta muốn tăng sức mạnh của chip nhưng trong "phạm vi cho phép về nhiệt độ, kích thước, điện năng tiêu thụ".

Quay lại vấn đề chính của hôm nay, CoW (chip-on-wafer) và SoW (system-on-wafer) là những cái tên mà TSMC đưa ra để giải quyết vấn đề khi mà transistor ngày càng khó thu nhỏ hơn trong khi nhu cầu chip mạnh hơn vẫn luôn tồn tại. Và câu hỏi trị giá ngàn tỷ USD ở đây (tin tôi đi, không có TSMC thì NVIDIA cũng không có ngày market cap được ngàn tỷ đâu) là làm sao tạo ra được con chip mạnh hơn? TSMC - đơn giản thôi, làm nó to hơn!

Chip MI300 của AMD to bằng cả bàn tay

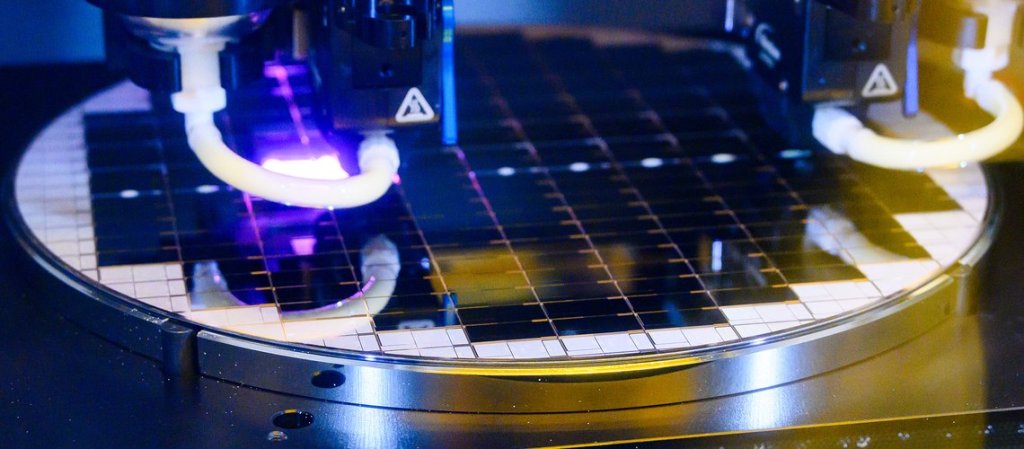

CoW hay cả con chip nằm trên wafer

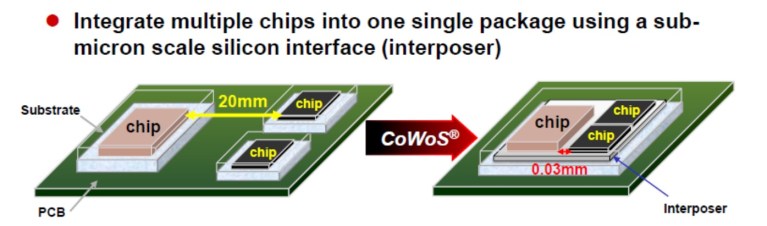

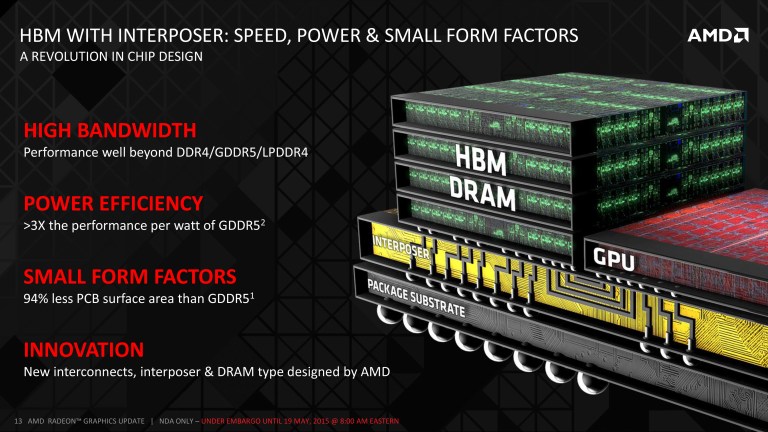

Trên thực tế, CoW hay CoWoS (chip-on-wafer-on-subtrate) đã xuất hiện từ vài năm trở lại đây, dưới hình hài của những con chip siêu đắt tiền như AMD R9 290X/MI300, NVIDIA A100/H100, Intel Gaudi 1/2/3. Bạn có thể thấy một motif chung của những sản phẩm này rất tương tự khái niệm chiplet của AMD - một con chip khổng lồ được ghép nối từ những chiplet nhỏ hơn. Điểm mấu chốt chính là lớp liên kết đệm (interposer) vốn sẽ kết nối tất các chiplet trên lại, trước khi gắn tất cả lên tấm PCB (subtrate). Vì thế, giới hạn của CoWoS sẽ là kích thước của tấm interposer.

Bản chất CoWoS là đặt tất cả die chip lên cùng 1 tấm interposer

Trong những năm vừa qua, TSMC liên tục tìm cách gia tăng kích thước interposer nhiều và nhiều hơn nữa. Hiện tại, interposer tối đa của công ty này đạt 80x80 mm (hoặc 1600 mm2), bự gấp đôi kích thước reticle dùng trong tiến trình EUV NA 0.33. Hãng này kỳ vọng tới 2026, có thể nâng interposer lên đến 100x100 mm (bự gấp 3,5 lần hiện tại), cho phép đặt được tới 5 con chip 800 mm2 cùng 12 con chip HBM lên đó. Có thể nói "con chip" lúc đó sẽ to gần bằng cái bánh tráng size 10 cm.

Mục tiêu của TSMC tới 2026 sẽ làm ra tấm interposer 100x100 mm

Nhưng đó chưa phải là giới hạn của sự "điên loạn"... Sẽ ra sao nếu bạn vẫn muốn "con chip" to hơn nữa? Bằng cái tô, cái chảo, cái bàn?

SoW hay siêu chip khổng lồ

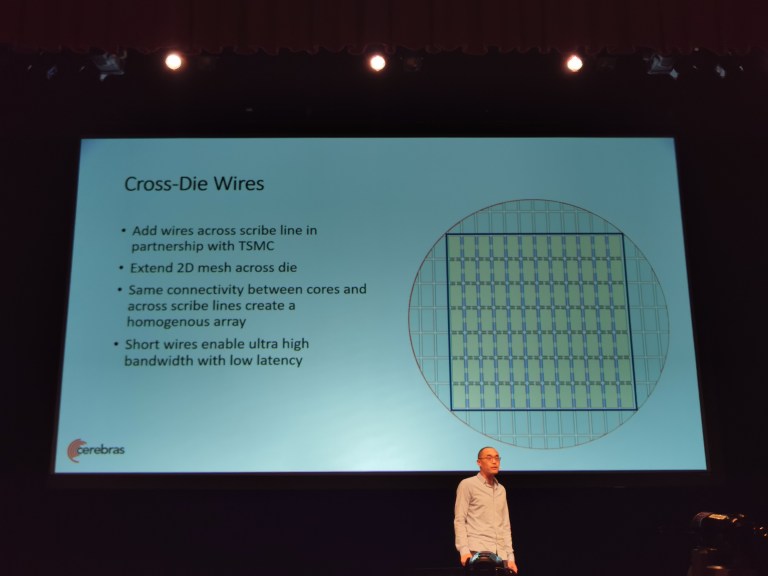

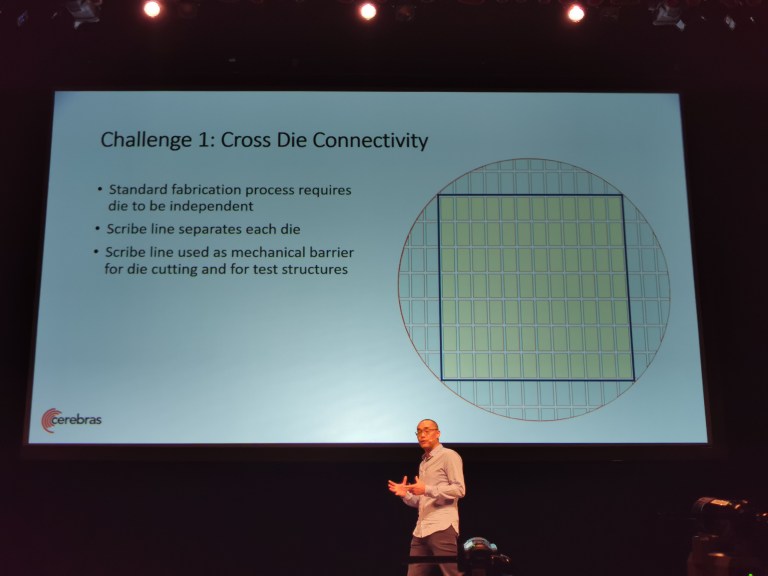

Đúng ra mà nói, đây không phải là lần đầu tiên SoW "chào sân". Quay lại 2019 (5 năm trước), tại hội nghị Hot Chips 31, Cerebras đã làm toàn bộ giới công nghệ phải miệng chữ Ô, mồm chữ O khi trình làng "con chip" bự bằng cái bếp điện (46.222 mm2) với 1.200 tỷ transistor được sản xuất trên tiến trình 16 nm! Và đoán xem ai đã "nấu" ra con chip này? Vâng, TSMC!

Tính tới 2019, Cerebras là con chip lớn nhất từng được sản xuất

Cerebras gọi đấy là con chip cấp wafer (wafer scale) vì nó được sản xuất từ đúng một tấm wafer! Để cho dễ hình dung, bạn hãy nghĩ từng die chiplet kia là một nhân CPU cũng được, và toàn bộ là 84 chiplet! Vì được làm trên cùng 1 wafer nên các die sẽ được nối mạch liên kết trực tiếp chứ không cần dùng tới interposer như giải pháp CoW đã nêu ở trên. Vì thế giới hạn của SoW chính là kích thước của tấm wafer. Tính tới hiện tại, wafer lớn nhất đang được dùng để sản xuất có size 300 mm. Đã có thông tin về wafer 450 mm song do chi phí quá đắt đỏ nên nó chỉ mới tồn tại ở giai đoạn nghiên cứu. Biết đâu liệu TSMC sẽ chuyển lên 450 mm khi "thời cơ chín muồi"?

Trên tay là cả một gia tài!

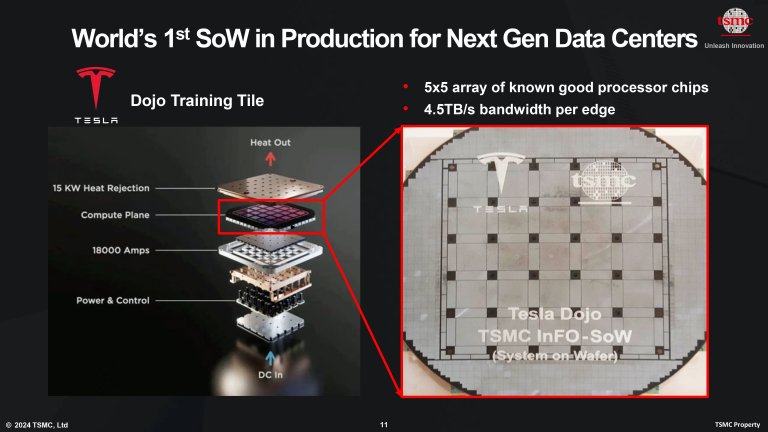

Quay về thực tại, SoW có thể nói vẫn còn đang ở những bước đi đầu tiên. Vì cho tới nay chỉ mới có 2 khách hàng dám "order" công nghệ này. Cerebras như đã nêu ở trên, và Tesla!

Hiện đại & hại điện

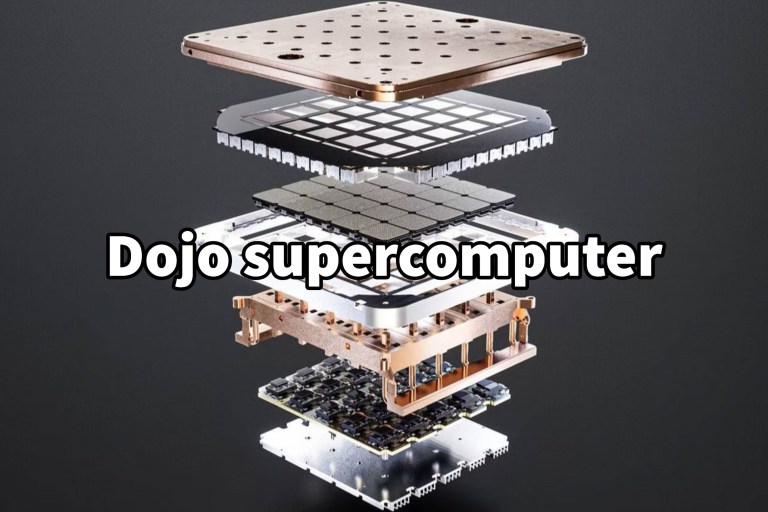

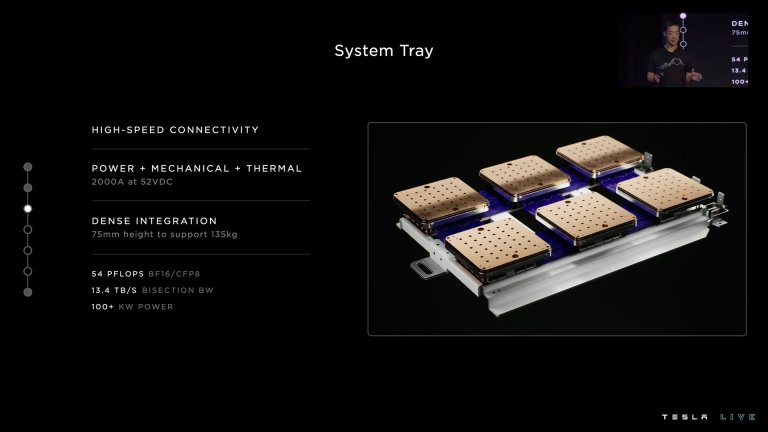

Cách đây không lâu Musk cho biết Tesla sẽ không phải là hãng xe hơi như chúng ta đã/đang/từng biết. Những tiết lộ từ TSMC cho thấy công ty của Musk sẽ chuyển hướng mạnh về AI. Mẫu chip cỡ wafer được TSMC nêu tên là Tesla Dojo D1 training tile. Theo công bố của Tesla, D1 training tile được tạo ra từ 25 con chip D1 riêng lẻ, mỗi chip có 354 nhân xử lý, cho tổng số 8.850 nhân xử lý trên toàn bộ tấm wafer trên.

25 chip Dojo D1 được sản xuất trên cùng 1 wafer 7 nm

Để "con chip" (nên gọi là "cục chip" hay "bánh chip" thì hợp hơn nhỉ?) này hoạt động sẽ khác 180 độ so với các chip SIP (system-on-package) mà chúng ta vẫn đang dùng. Trước hết, nó cần dùng một tấm nền (subtrate) đặc biệt vì lượng điện cần cấp vào cực kỳ nhiều (18.000 Amps). Không rõ hiệu suất sử dụng năng lượng bao nhiêu nhưng D1 training tile cần một tấm tản nhiệt đạt công suất 15 kW! Để cho tiện hình dung, bếp hồng ngoại chúng ta dùng hiện nay có công suất tối đa khoảng 2 kW cho một bếp. Vậy đây là một cái "lò chip"...

Và Cerebras là Tesla Dojo D1 là 2 sản phẩm khởi đầu cho SoW. Hiện tại chúng chỉ tận dụng được phần hình vuông/chữ nhật nằm ở chính giữa wafer (do bản chất hình học của reticle). 4 góc tròn còn lại đang bị bỏ phí. Trong tầm nhìn của TSMC, các góc tròn này có thể được tận dụng để gắn thêm các chip nhớ, IO... thậm chí là liên kết vật lý (connector) với các wafer khác. Nhưng đó sẽ là mục tiêu xa hơn trong khoảng 2026-2027. Đồng thời cũng sẽ đẻ ra nhiều thách thức hơn cả về nhiệt độ, điện năng tiêu thụ, vân vân và mây mây...

Những con chip cấp wafer này sẽ không bao giờ được bán phổ thông

Song một điều chắc chắn - những "bánh chip" SoW sẽ không bao giờ xuất hiện trên các sản phẩm tiêu dùng phổ thông. Trước hết chi phí làm ra chúng có thể đắt hơn cả một căn nhà hoặc hơn. Sau đó là chi phí đóng gói, tản nhiệt, vận hành. Hiển nhiên một thiết bị tiêu thụ tới 18 kW sẽ đòi hỏi một lưới điện chuyên biệt và dĩ nhiên, cả một hệ thống tản nhiệt mà chỉ các datacenter mới dám đầu tư.

Theo TSMC

3 thoughts on “Công nghệ làm chip TSMC CoW-SoW và sự 'điên loạn' của ngành bán dẫn”