TSMC - Hiệu suất dây chuyền 2 nm ổn định, sản xuất hàng loạt trong 2025

Hiện tại gần như không ai có thể cản được đà tiến của công ty Đài Loan.

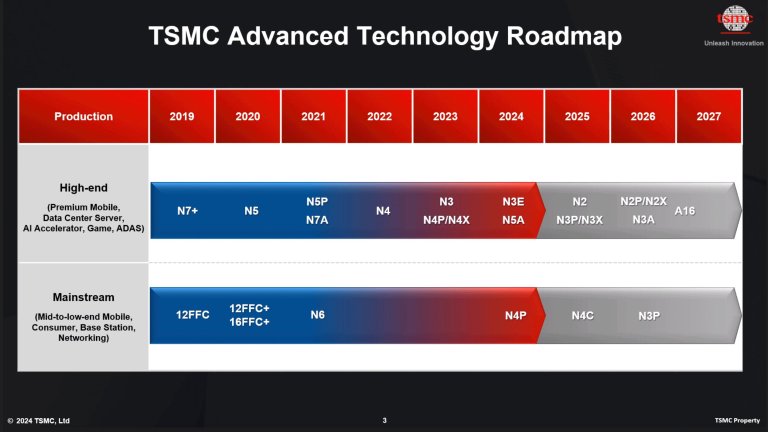

Trong khi dây chuyền 3 nm (N3) đi vào sản xuất tương đối lâu, nhiều người đang quan tâm đến việc node 2 nm (N2) của TSMC hiện đã đạt đến mức độ nào, liệu sắp khai thác được hay chưa. Tại Symposiums 2024, công ty Đài Loan không quên "nhắc nhẹ" tới điều này. Theo đó, mọi thứ đang đúng tiến độ, nửa sau 2025 là đã có thể đưa N2 vào sản xuất.

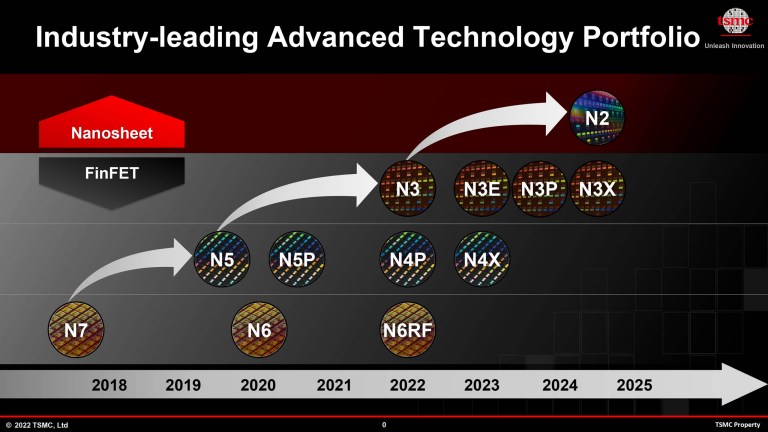

Một chi tiết cần nhắc lại là N2 là dây chuyền đầu tiên áp dụng kỹ thuật GAAFET của TSMC, rất khác so với kỹ thuật FinFET đang được áp dụng cho N3. Vì thế sẽ có không ít trở ngại khi chuyển đổi. Samsung là công ty đầu tiên áp dụng GAAFET trên 3 nm và hiệu suất không mấy khả quan.

Hiện tại, các chi tiết transistor GAAFET của TSMC đang đạt 90% mức hiệu năng được kỳ vọng. Còn hiệu suất các chip SRAM 265 Mb (32 MB) đã vượt 80%, tuỳ theo lô sản phẩm. Trước đó, hồi tháng 3 này, hiệu suất SRAM vào khoảng 70%. Còn tầm giờ này năm ngoái, nó mới ở mức 35%. Hiện tại hiệu năng các mạch điện đã cho phép đạt tần số hoạt động cao hơn trước nhưng mức tiêu thụ điện vẫn được giữ nguyên.

Các khách hàng của TSMC hiện rất quan tâm tới dây chuyền GAAFET này. Số lượng mẫu thiết kế cuối (tape-out) mới được đặt hàng cho N2 đã nhiều gấp đôi so với node N5 (lúc vừa ra mắt). Điều này cho thấy mức độ cạnh tranh dữ dội giữa các công ty như Apple, AMD, NVIDIA, Qualcomm... khi ai cũng muốn chiếm lĩnh thị phần trước tiên.

Ngoài ra, TSMC cho biết sang 2026, công ty này sẽ giới thiệu tiếp node N2P. So với node N3E, N2P dự kiến cho phép xung nhịp tăng 15 ~ 20%, hoặc giảm tiêu thụ điện 30 ~ 40%, đồng thời gia tăng mật độ transistor gấp 1,15 lần. N2P sẽ không áp dụng BSPDN mà sẽ dành cho node A16 kế sau đó.

Theo AnandTech

3 thoughts on “TSMC - Hiệu suất dây chuyền 2 nm ổn định, sản xuất hàng loạt trong 2025”