Tìm hiểu công nghệ AMD 3D V-Cache - Sản xuất như thế nào?

Mặc dù lý thuyết cache bự ai cũng biết, nhưng làm sao để ra sản phẩm thực tế là cả vấn đề…

Ở phần trước, chúng ta đã nói về lý thuyết cách mà bộ nhớ cache vận hành cũng như lợi ích/nhược điểm của nó. Có thể nói bất kỳ công ty sản xuất chip nào cũng hiểu những vấn đề này. Nhưng làm sao để triển khai nó trong thực tiễn thì lại là vấn đề khác. Một câu quen thuộc hầu như ai cũng từng nghe qua là "nói thì dễ hơn làm".

Mình cũng đã từng nêu, cấu trúc SRAM không có gì quá phức tạp vì hàng chục năm qua nó vẫn vậy. Vấn đề lớn nhất ở đây là SRAM tốn rất nhiều transistor (T) để làm ra. Loại SRAM phổ thông hiện tại cần tới 6T chỉ để chứa 1 bit dữ liệu! Để tiện so sánh, bộ nhớ DRAM chỉ tốn 1T và 1 tụ điện để chứa 1 bit dữ liệu. Tất nhiên chúng ta vẫn có những kiểu SRAM tốn ít hoặc nhiều transistor hơn 6T, song chúng ít được xài hơn nên tạm không truy xét.

Nội dung bài viết

Cơn "hấp hối" của SRAM

Nhưng hao tổn transistor/silicon chỉ là 1 mặt của vấn đề. Một vấn đề khác "nghiêm trọng" hơn là trong những năm trở lại đây, việc thu nhỏ tế bào SRAM đã khó khăn hơn trước rất nhiều. Nếu các mạch logic (CPU, GPU, DSP…) thu nhỏ tương đối tốt sau mỗi tiến trình bán dẫn thì bộ nhớ nói chung lại không được như vậy. Có một thực tế là không chỉ SRAM mà cả DRAM hay NAND cũng không tăng mật độ dữ liệu hơn trước là bao. Nếu để ý, bạn sẽ thấy các tiến trình sản xuất DRAM/NAND tiên tiến nhất hiện nay vẫn đâu đó ở 10 nm hoặc lớn hơn.

So sánh kích thước SRAM của các hãng theo từng năm (TSMC màu cam). Có thể thấy mặc dù có nhỏ đi thật nhưng chênh lệch này cứ giảm dần. Riêng TSMC N3P bự ngang TSMC N5!

Tại hội nghị IEDM 2022, TSMC đã khiến cả giới bán dẫn nhảy dựng lên khi công bố kích thước tế bào SRAM của tiến trình N3. Cụ thể trong khi mật độ mạch logic N3 cao gấp 1.6 lần mạch N5, thì mật độ SRAM chỉ "nhích" lên 5% (33.55 vs. 31.8 Mb/mm^2)! Tệ hơn, phiên bản N3E (nâng cấp của N3) có mật độ SRAM bằng đúng N5 (31.8 Mb/mm^2). Có nghĩa 32 MB SRAM ở N5 có kích thước bao nhiêu thì sang N3E không có gì thay đổi!

May thay trong thông tin mới đây nhất về tiến trình N2 (sẽ đi vào sản xuất trong nửa cuối 2025), TSMC cho biết mật độ SRAM của N2 sẽ tăng lên đáng kể, ở mức 38 Mb/mm^2. Tuy vậy, khả năng này đạt được nhờ N2 đã chuyển sang cấu trúc GAAFET nhỏ gọn hơn FinFET. Nhưng GAAFET không phải lá bài vĩnh cửu. Thực tế là khả năng thu nhỏ transistor đang càng lúc càng khó hơn. Thế nên trong một tương lai xa hơn thì việc mật độ SRAM "dậm chân tại chỗ" vẫn luôn ám ảnh các công ty thiết kế chip.

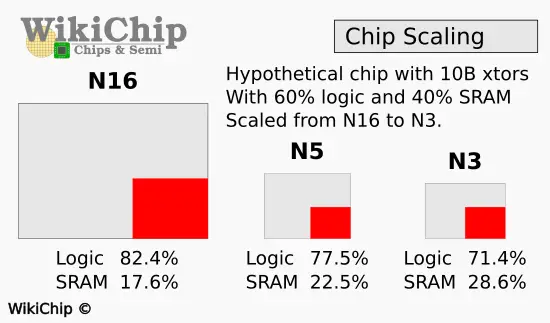

Một thiết kế chip giả định 10 tỷ transistor dựa trên 3 tiến trình N6, N5 và N3. Có thể thấy phần SRAM chiếm ngày càng nhiều hơn sao mỗi tiến trình

Tất nhiên TSMC không phải công ty duy nhất có thể sản xuất chip bán dẫn. Song với việc Intel lẫn Samsung đang "hì hục" theo sau công ty Đài Loan thì đây là một viễn cảnh khá u ám cho giới công nghệ. Hiện tượng này có nghĩa là nếu muốn tăng thêm số nhân xử lý (mạch logic) cho các con chip tương lai, các công ty thiết kế chip phải cân nhắc liệu có phải tăng kích thước die chip (để giữ nguyên dung lượng cache/nhân) hoặc giảm bớt dung lượng cache/nhân (để giữ die chip không phình ra). Đau đầu lắm đấy!

Đây cũng là lý do tại sao dù con chip bự nhất hành tinh WSE-3 của Cerebras mặc dù có tới 4000 tỷ transistor N5 nhưng số nhân và SRAM của nó tăng không bao nhiêu so với phiên bản WSE-2 ra mắt trước đó chỉ có 2600 tỷ transistor N7 (900,000 vs. 850,000 nhân và 44 vs. 40 GB SRAM), vì phần lớn số transistor có thêm này chủ yếu để "đắp" vào SRAM.

Kích thước cache trở thành mối lo âu của nhiều công ty chip như AMD

Chia hộ khẩu để tốt hơn

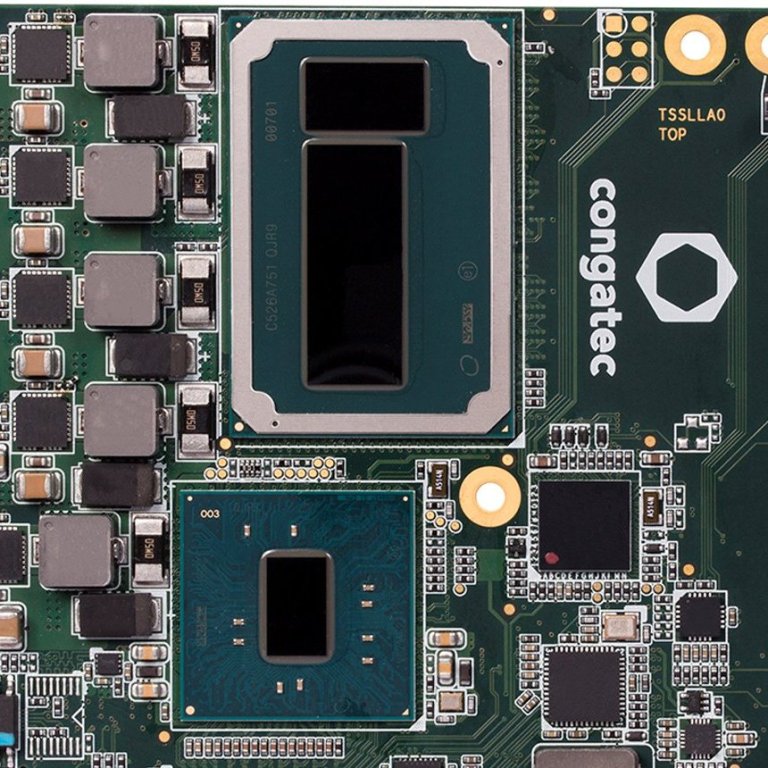

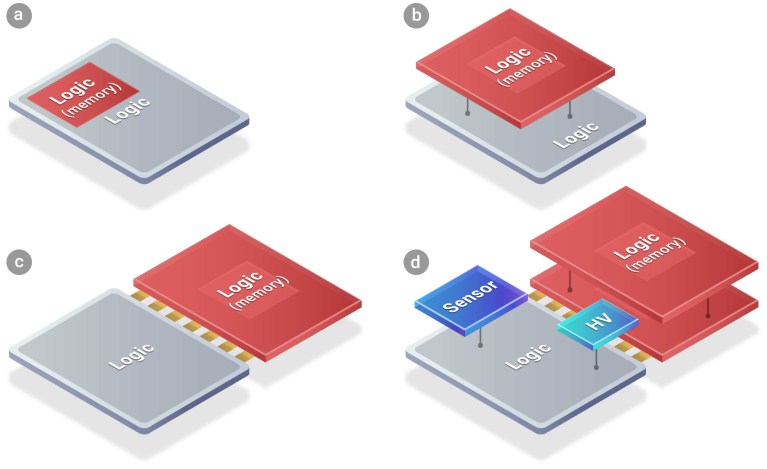

Từ vấn đề thu nhỏ SRAM nêu trên, các kỹ sư bán dẫn bắt đầu suy nghĩ những phương pháp khác nhau để cải thiện tình hình. Một trong các cách đó là thiết kế nhiều die (MCM hoặc chiplet). Trên thực tế thì hướng đi này không hề mới. Những con chip như POWER7 của IBM hay PlayStation 2 của Sony hay Haswell của Intel đều kèm theo một (số) die chip nhớ bên cạnh die CPU. Khác biệt ở đây chúng không phải SRAM mà là DRAM (hay eDRAM).

Nhưng nhắc lại các ví dụ trên không phải để nói AMD cũng làm y chang họ, mà ở mặt ý tưởng - SRAM hoàn toàn có thể không nằm cùng die với CPU.

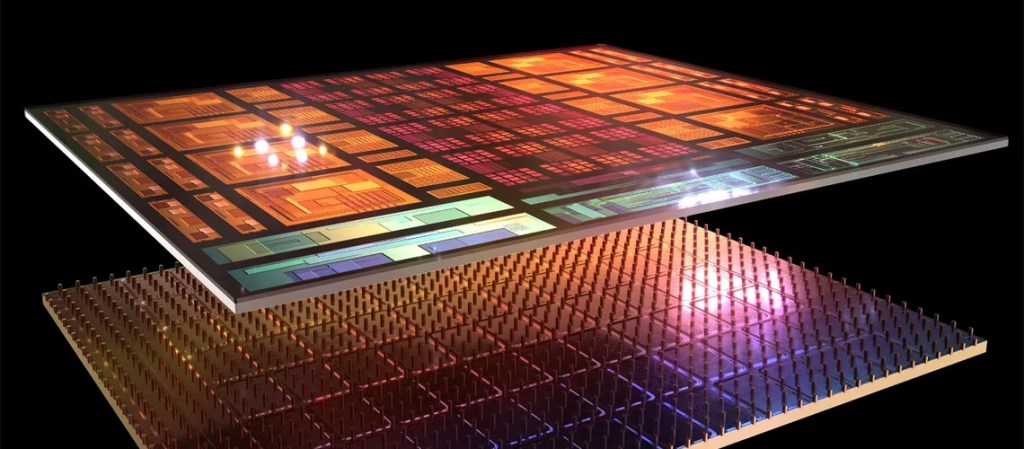

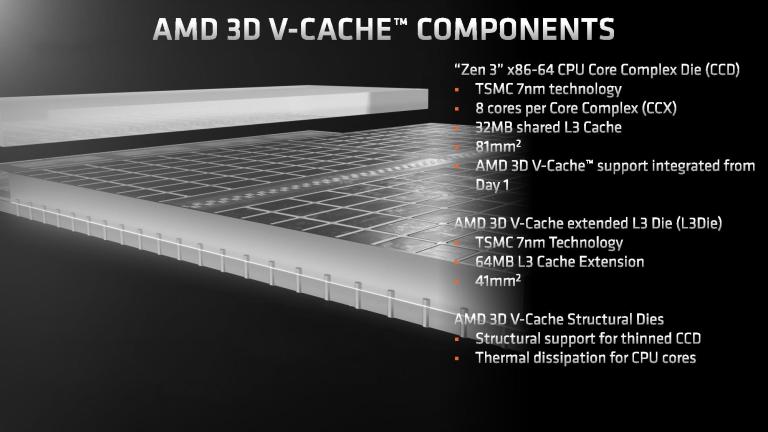

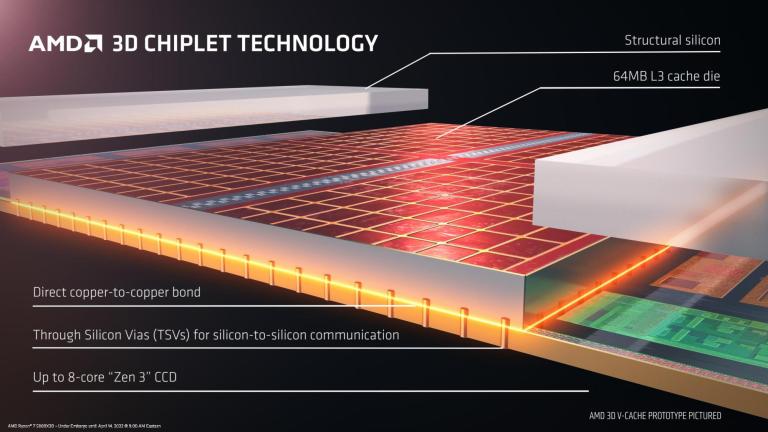

AMD 3D V-Cache "đời đầu" với die X3D nằm trên die CCD

Như đã nêu ở trên, mạch SRAM và mạch logic bắt đầu xuất hiện sự chia rẽ. Sự bất đồng về hệ số thu nhỏ kích thước này dẫn tới việc SRAM ngày càng chiếm nhiều diện tích hơn. Mà xu hướng này cứ kéo dài thì tới một lúc phần lớn "đất" làm chip sẽ chỉ toàn SRAM. Hay nói cách khác là hiệu năng chip đời sau sẽ tăng nhỏ giọt vì các công ty không thể nhồi nhét được nhiều nhân xử lý hơn mức quota silicon còn lại được.

Vậy là SRAM phải "ra đi". Hay đúng hơn là "một phần" (không thể bỏ toàn bộ SRAM ra khỏi mạch logic được) SRAM sẽ không cùng die với CPU nữa.

Từ đây xuất hiện một cách nghĩ khác về SRAM - chúng có thể được sản xuất trên tiến trình cũ hơn nếu như việc thay đổi node bán dẫn không có lợi (với SRAM). Vì tiến trình cũ thường có hiệu suất tốt hơn mà giá thành cũng rẻ hơn các tiến trình mới. Như thế, giá thành chung sẽ thấp hơn so với việc dồn hết SRAM và mạch logic vô cùng một die chip (dùng tiến trình mới nhất).

Nhưng "cắt khẩu" thôi chưa đủ. Vì vấn đề đơn giản như thế thì các công ty khác cũng đã áp dụng với SRAM chứ không phải chỉ dừng lại ở DRAM. Tại sao?

Có thêm eDRAM cũng tốt, nhưng không đủ tốt về độ trễ khi là thiết kế chiplet 2D

Vấn đề ở khoảng cách. Hãy nhớ ví dụ nhà máy ở phần trước. Nếu DRAM như một cái kho nằm ở cảng vụ cách hàng km thì SRAM là đống pallet chỉ cách xưởng sản xuất có vài mét/vài chục mét. Nếu SRAM cũng nằm ở 1 die riêng rẽ như eDRAM thì lợi ích trở nên nhạt nhoà - mạch điện quá dài dẫn tới độ trễ quá cao. Nói cách khác, kể cả có khác die thì yêu cầu vẫn phải là độ trễ cực thấp - 2 die mà phải như 1 die! Làm thế nào???

AMD 3D V-Cache hay TSMC SoIC

Một điều có thể nói về AMD là dù công ty này không phải khách hàng "sộp" nhất, chịu chi đậm như Apple hay NVIDIA, nhưng là công ty "chịu chơi" nhất của TSMC. Những công nghệ bán dẫn mới nhất của TSMC hầu như đều được AMD áp dụng sớm nhất vô sản phẩm của mình, mà SoIC (theo cách của TSMC) hoặc 3D V-Cache (cách của AMD) là ví dụ.

3D V-Cache dựa trên công nghệ SoIC của TSMC

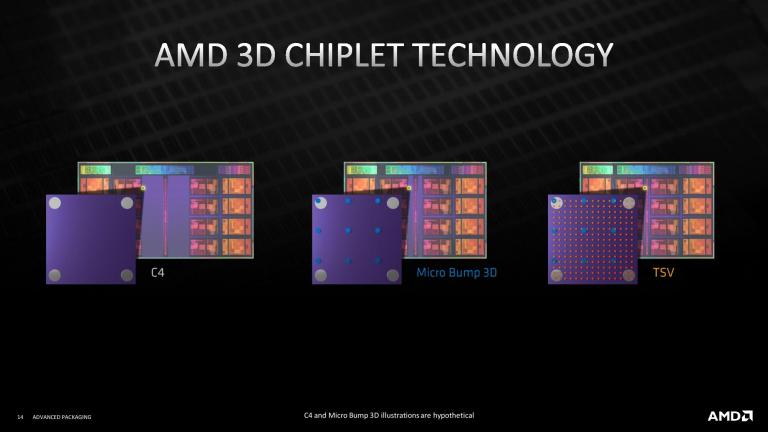

Đơn giản mà nói, SoIC là giải pháp liên kết các die chip lại với nhau theo chiều dọc, thông qua các "chiếc thang" TSV (through silicon vias). Để tiện hình dung thì bạn có thể so sánh với nhà cao tầng, tầng dưới là xưởng A thì tầng trên là xưởng B hay kho, cũng được. Nhưng TSV thực ra cũng không phải khái niệm mới trong bán dẫn. Mọi con chip NAND được sản xuất hiện nay đều xài TSV để chồng die. Vậy SoIC có gì đặc biệt?

Một yếu tố không thường được nói tới trong các con chip là các mạch điện liên kết các thành phần lại với nhau. Các con chip đời sau mạnh hơn đời trước đơn giản vì số lượng các thành phần nhiều hơn trước (tương ứng với số transistor). Nhưng nhiều thành phần hơn cũng đồng nghĩa chúng cần có nhiều liên kết hơn. Hiểu nôm na như đường chúng ta đi năm xưa kẹt xe không nhiều vì số lượng phương tiện ít, nay cứ bước ra đường là kẹt xe vì mật độ phương tiện tăng lên quá nhiều, hạ tầng không theo kịp dân số. Chip cũng thế. Tất nhiên trong một thiết kế monolithic thì không ai nói tới vì tự các kỹ sư đã "quy hoạch sẵn" từ trước.

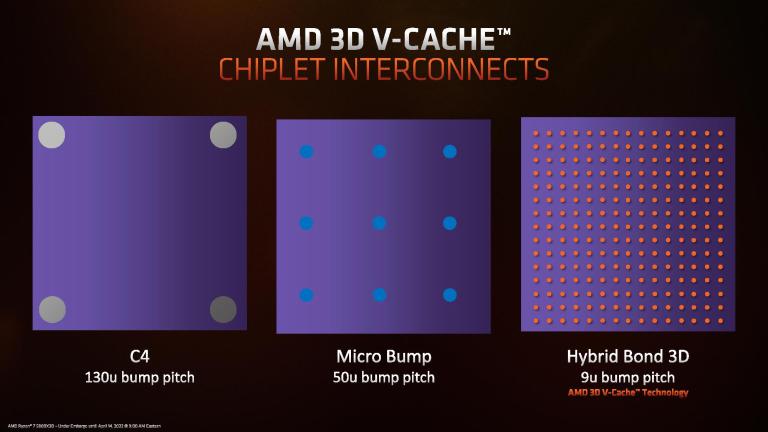

So sánh 3 kiểu liên kết die chiều dọc C4, microbump và Bond 3D. Mật độ liên kết càng cao mới đáp ứng được nhu cầu trao đổi điện năng - tín hiệu giữa các die

Song khi qua chiplet, vấn đề phức tạp hơn khi mật độ transistor tăng lên (tiến trình mới hơn) mà mật độ TSV vẫn như cũ thì "kẹt xe" là chuyện sớm muộn. TSV phải giảm kích thước thì mới có dư địa để chồng chip! Đây chính là khác biệt của SoIC. Tính tới 2022, TSMC đã có khả năng tạo ra mạng lưới TSV siêu nhỏ với khoảng cách (pitch) giữa từng "lỗ" TSV chỉ có 9 micromet! Tới 2024, công ty này kỳ vọng thu nhỏ con số trên còn 6 micromet và tới 2027 chỉ còn 3 micromet! So với TSV phổ thông, cự ly giữa 2 lỗ TSV trung bình lên tới 130 micromet! Chỉ có tăng mật độ TSV lên thì mới có hy vọng chồng chip hiệu quả khi mật độ mạch logic ngày càng tăng.

Dễ hình dung là trước nay bạn cần phải ra thang máy hay cầu thang để xuống tầng dưới. Còn nay mỗi line sản xuất hay ô làm việc có sẵn cầu tuột và dây leo, bạn cứ trượt xuống là được!

TSMC làm SoIC như thế nào?

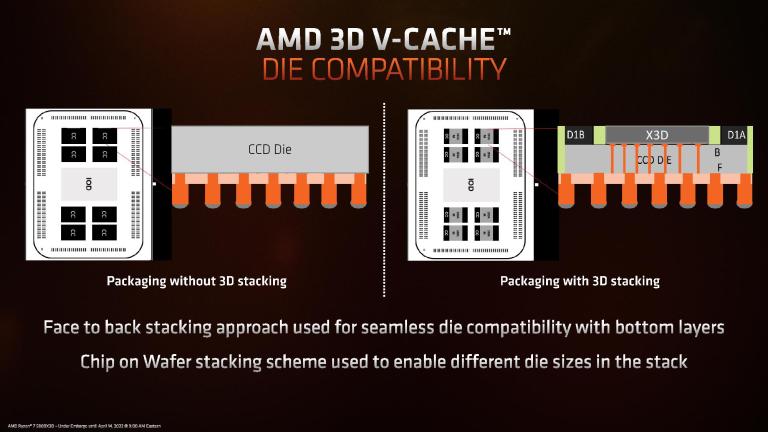

Nhưng chắc bạn cũng biết, chuyện gì cũng có 2 mặt. Không có gì free cả. Để ô làm việc nào cũng có cầu tuột xuống dưới, đòi hỏi bản vẽ thiết kế phải chuẩn bị sẵn "tâm lý" ngay từ đầu. Bạn không thể cứ đục cái lỗ giữa 2 die chip đã có từ trước rồi tắt máy đi ngủ. Để áp dụng SoIC vào sản phẩm đòi hỏi AMD phải theo sát TSMC ngay từ đầu. Thực tế từ Zen 3, mọi thiết kế CCD của AMD đều áp dụng "chừa đất" làm TSV. Đây là lý do tại sao có những sản phẩm khác của công ty này không có/không thể áp dụng 3D V-Cache - vì ngay từ thiết kế chúng đã không có TSV! Tính tới hiện tại, AMD chỉ show 3D V-Cache trên CCD, chưa thấy thiết kế monolithic nào có công nghệ này.

Để áp dụng SoIC, mọi die Zen 3 trở đi của AMD phải được thiết kế hỗ trợ TSV ngay từ đầu

Và có một điểm quan trọng khác nữa ở SoIC - nó dùng tiếp xúc trực tiếp giữa các mối đồng (Cu) thay cho mối hàn chì/thiếc quen thuộc ở microbump mà chúng ta thường gặp ở các chip BGA. Lý do đơn giản là vì ở cự ly chỉ có 9 micromet mà có tới hàng trăm điểm như thế, làm sao để hàn vừa nhanh, vừa chính xác? Hàn chậm quá sẽ ảnh hưởng tới năng suất cuối dây chuyền và sản lượng sẽ thấp >> chi phí X3D sẽ cao. Vì thế TSMC chuyển sang một kiểu "hàn" khác.

Chúng ta không rõ chi tiết cách làm thế nào, nhưng nhìn chung có 3 giai đoạn như này. Đầu tiên, mặt tiếp xúc giữa 2 die chip được mài bóng tới mức gần như không còn khoảng cách. Sau đó, 2 die này được đặt lên nhau sao cho độ lệch TSV giữa 2 die còn dưới vài micromet. Giai đoạn kế là "hàn ướt" (hydrophilic) giữa 2 bề mặt điện môi với nhau ở nhiệt độ thường, rồi chuyển qua gia nhiệt để cố định 2 die chip. Cuối cùng mới là tạo ra liên kết Cu-Cu trực tiếp giữa 2 die thông qua hiệu ứng phân tán nguyên tử thể rắn. Toàn bộ quá trình khá phức tạp song ưu điểm là nó không phân biệt kích thước TSV (có thể áp dụng cho các thế hệ sau) và có thể sản xuất quy mô lớn, đồng nghĩa với giá thành không tăng lên nhiều.

Liên kết Cu-Cu trực tiếp không dùng mối hàn. Do đó 2 die phải được mài cực phẳng và phải được canh lề cẩn thận trước khi liên kết vĩnh viễn với nhau

Ngoài ra vấn đề lợi ích về sản lượng ra, phương pháp "hàn" Cu-Cu trực tiếp kia còn một ưu điểm khác là nó tiêu thụ ít điện năng hơn so với microbump. Lý do đơn giản thôi, mạch điện càng dày thì điện trở càng nhiều, điện trở nhiều thì công suất nhiệt cao và hao tổn nhiều hơn. AMD cho biết liên kết Cu-Cu xài ít điện hơn microbump gấp 3 lần. Cũng đáng cân nhắc.

Cũng cần nói thêm 3D V-Cache chỉ là 1 ứng dụng của SoIC, khi chồng chip nhớ lên chip logic. Trong tầm nhìn của TSMC thì nó bao gồm cả chồng die logic lên logic, như một mẫu bản quyền SoC mà AMD vừa đăng ký. Mình sẽ có bài viết rõ hơn về năng lực này của TSMC.

Mạch điện càng nhỏ càng ít điện trở. Không có mối hàn lại càng dẫn điện tốt hơn

3D V-Cache đời 1, 2 và 3

Theo thuật ngữ của AMD thì công ty này chỉ mới có 2 thế hệ X3D, trong đó Zen 5 đang dùng thế hệ thứ 2. Còn Zen 3 và 4 xài chung thế hệ 1. Song mình cho rằng X3D trên Zen 4 vẫn đáng được xem là 1 thế hệ vì nó có những khác biệt so với Zen 3, hoặc ít nhất là thế hệ 1.5 🙂 Lý do trước hết là X3D trên Zen 4 có băng thông cao hơn Zen 3 (2.5 vs. 2 TB/s) (ngày nay hiệu năng hơn đời trước 25% là cao rồi).

2 thế hệ Zen 3 và 4 đều có die X3D nằm ở trên. Hãy để ý die này bé die CCD nên cần có 2 khối silicon "mù" chống đỡ

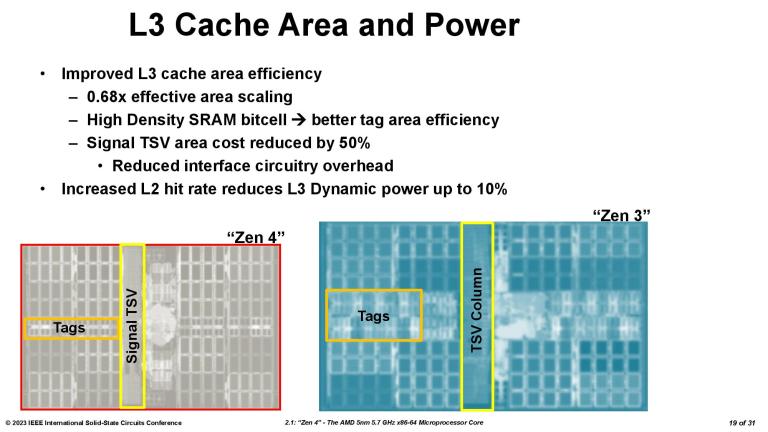

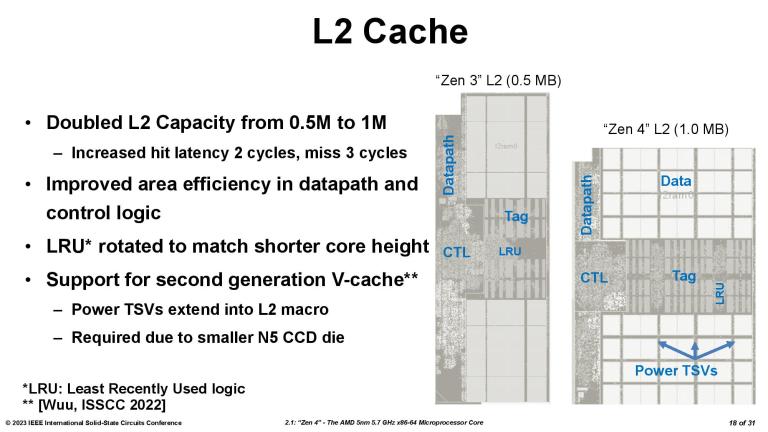

Sau nữa là die X3D ở Zen 4 nhỏ hơn die X3D Zen 3 (36 vs. 41 mm2), mặc dù đều cùng dùng tiến trình TSMC N7 và cùng số lượng transistor (4.7 tỷ). Đây là điều thú vị nói thêm vì die CCD Zen 3 dù cũng là N7 nhưng kích thước lại lớn hơn (80.7 mm2) dù có ít transistor hơn (4.15 tỷ). Lý do ở đây vì mạch logic có rất nhiều loại thư viện IC khác nhau, trong khi SRAM thì tính chất đồng nhất nên dễ sắp xếp sao cho gọn gàng hơn. Và điều đáng nói tiếp theo là dù cùng là 4.7 tỷ transistor như X3D Zen 4 lại nhỏ hơn, cho thấy AMD đã sử dụng thư viện SRAM có mật độ dày đặc hơn bản Zen 3.

Sau cuối là tuy đều là cache như nhau, nhưng mạch tín hiệu TSV của Zen 4 lại khác với Zen 3. Tại sao? Nguyên do ở chỗ die CCD Zen 4 có kích thước bé hơn Zen 3 (66.3 vs. 80.7 mm2) dù có nhiều transistor hơn. Chi tiết này khiến cho die X3D ở Zen 4 không những che hết phần L3 cache trên CCD mà còn lấn qua L2 cache, dẫn tới việc các kỹ sư AMD phải thiết kế lại đường điện TSV trên Zen 4.

So sánh kích thước cache trên CCD Zen 3 và 4. Có thể thấy ở Zen 4, kỹ sư AMD phải bổ sung thêm phần cấp điện TSV cho die X3D nằm ở trên

Và dù X3D Zen 3, 4 có nhiều khác biệt đến vậy, công ty này vẫn gọi chung là 3D V-Cache thế hệ 1 🙂

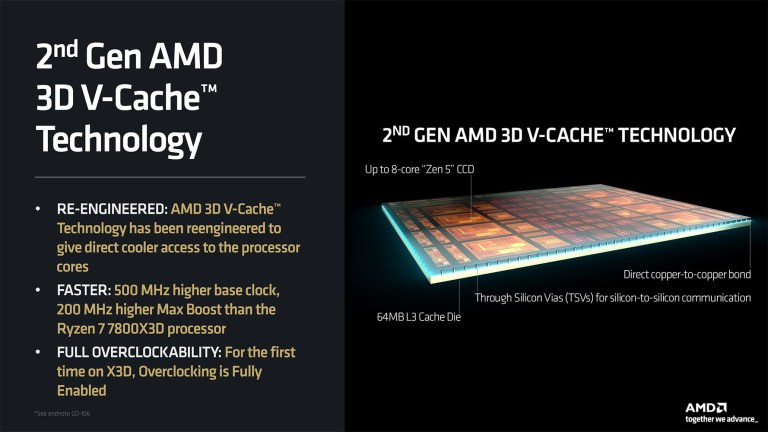

Đến Zen 5 hay Ryzen 7 9800X3D như bạn đã biết, AMD gọi đấy là 3D V-Cache thế hệ 2. Cũng đúng thôi vì nó thực sự khác đời 1. Một trong các nhược điểm của bản cũ là die X3D nằm phía trên die CCD. Điều này hạn chế phần nào việc tiếp xúc với IHS của CCD và nó thoát nhiệt chậm hơn phiên bản không X3D. Vì lẽ đó nên nếu bạn có để ý, các chip X3D Zen 3, 4 của AMD đều có xung nhịp thấp hơn phiên bản không X3D. Mà xung thấp hơn thì ứng dụng nào "yêu" xung sẽ bị ảnh hưởng. Có thêm cache mà giảm hiệu năng, sao buồn quá?

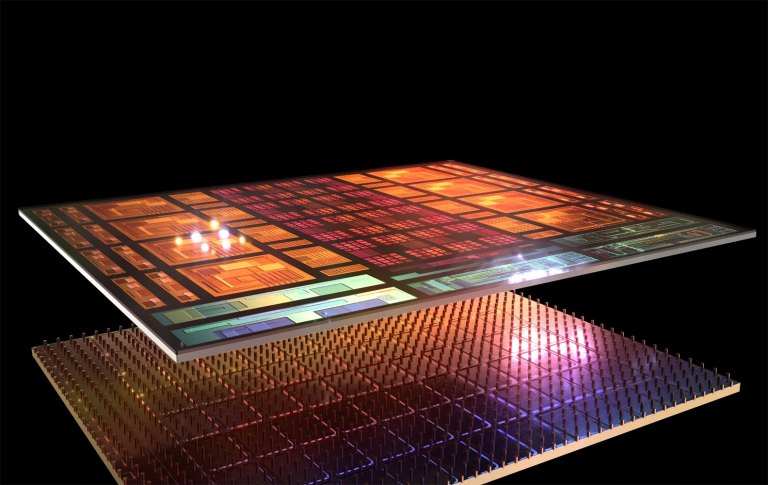

Rút kinh nghiệm từ hạn chế này, các kỹ sư AMD quyết định mang die X3D xuống bên dưới die CCD. Bằng cách này die CCD sẽ tiếp xúc trực tiếp với IHS và ô là la! Hạn chế về xung nhịp không còn nữa, toàn bộ 8 nhân Zen 5 có thể chạy hết công suất mà không sợ bị quá nhiệt như 2 thế hệ đàn anh. Song để làm được điều đó đòi hỏi có những thay đổi không chỉ riêng die X3D mà cả die CCD.

3D V-Cache thế hệ 2 của AMD. Hãy để ý kích thước die X3D mới bự bằng die CCD Zen 5 vì nó phải cung cấp cả điện cho die này

Trước hết, die nào nằm dưới thì die đó sẽ đóng cả vai trò truyền tải điện năng và tín hiệu cho die ở trên, cụ thể là die CCD. Có nghĩa die X3D bây giờ không bé nhỏ như trước (chỉ bao quanh L3 cache) mà sẽ to hơn hoặc bằng die CCD. Tất nhiên chỉ phần nào làm SRAM thì mới được "vẽ mạch" in, còn lại chỉ để "đục lỗ" TSV để kết nối CCD với PCB ở dưới. Nhìn theo kiểu nào đấy thì die X3D cũng gần tương tự lớp interposer có trên các sản phẩm khác. Do đó kích thước die X3D Zen 5 tăng lên đáng kể, tuy AMD không công bố chi tiết nhưng ta có thể xem như nó bự bằng die CCD - 70.6 mm2. Nhưng vì phần cache mới là quan trọng nhất (cho là kích thước không đổi so với Zen 4), nên có thể đoán hiệu suất bán dẫn cũng không tăng hơn là bao (vì phần silicon còn lại chỉ để chứa TSV và chống đỡ die CCD, nên rủi ro bị lỗi cũng thấp).

Do mục đích của 3D V-Cache thế hệ 2 chỉ là để die CCD tiếp xúc trực tiếp với IHS, nên về cơ bản không có mấy khác biệt hiệu năng so với 3D V-Cache thế hệ 1. Nếu có khác chăng là xung nhịp CCD được "mở" và hệ quả như bạn đã biết, 9800X3D đang là con chip chơi game tốt nhất hành tinh.

Đến đây chúng ta hiểu cách AMD làm ra X3D như thế nào. Ở phần sau, mình sẽ bàn về tương lai của công nghệ này cũng như những ý nghĩa khác nó có thể mang lại (ngoài game).

3 thoughts on “Tìm hiểu công nghệ AMD 3D V-Cache - Sản xuất như thế nào?”