Phân tích kiến trúc CPU Intel Lunar Lake - Tỉnh giấc sau đêm dài (P1)

Sau nhiều năm liền ngủ quên để các đối thủ lần lượt vượt mặt, gã khổng lồ x86 nay đang tăng tốc một cách chóng vánh.

Năm 2024 này dường như là một dấu mốc quan trọng trên thị trường vi xử lý toàn cầu, khi các đại diện ARM (RISC) đang tỏ ra thắng thế với những cái tên Apple và Qualcomm. Bản thân AMD tuy cũng khả quan hơn Intel song với đặc trưng kiến trúc x86 (CISC), tương lai về việc kiến trúc nào sẽ được giới công nghệ ưu ái là cuộc đấu trí mà mọi CEO các công ty chip sẽ phải đau đầu tính toán. Bản thân con chip Lunar Lake (LNL) được bàn trong hôm nay chỉ là một mảnh ghép về mặt lâu dài.

Nội dung bài viết

Sơ lược thị trường vi xử lý nhiều năm qua

Về cơ bản mà nói, cho tới 2015 trở về trước đó, có thể chia x86 và ARM ra 2 phân khúc máy tính (khổ lớn) và di động (cầm tay) hoặc thiết bị nhúng. Xu thế sản phẩm này dẫn tới kiểu suy nghĩ rập khuôn (stereotype) là x86 chỉ phù hợp với ai cần sức mạnh tính toán còn ARM chỉ dành cho tiết kiệm điện. Tư duy này không hẳn sai nhưng cho thấy sự hiểu biết không đầy đủ về bản chất x86 lẫn ARM.

Intel Atom từng được dùng trên smartphone Android nhiều năm trước, nhưng chạy giả lập nên hiệu năng rất thấp

Trên thực tế, x86 vẫn có thể tiết kiệm điện và ARM vẫn có thể dùng cho hiệu năng cao. Ví dụ điển hình như Intel Atom Z từng dùng trên một số mẫu smartphone Android nhiều năm trước. Song nó đã không thành công và có 3 nguyên nhân chủ đạo. Trước hết là sự cạnh tranh quá gay gắt từ các đối thủ ARM, hầu như các brand Android phổ biến chỉ dùng chip Qualcomm, Samsung hoặc MediaTek. Sau đó là việc phải chạy giả lập vì nhiều ứng dụng Android chỉ được viết cho ARM, khiến cho hiệu năng bị tụt giảm. Cuối cùng là Intel không mạnh về hạ tầng viễn thông (Intel mạnh Wi-Fi, Bluetooth nhưng bước sang 2G/3G/4G là sân nhà của Qualcomm, Broadcom...). Kết cục là Atom Z bị "vùi dập tơi tả" vì không tạo ra được hệ sinh thái đủ mạnh trên di động.

Qua tới ARM, thực tế cho thấy kiến trúc này vẫn có thể cho sức mạnh cao khi cần thiết. Ví như siêu máy tính Fugaku của Nhật từng đứng đầu TOP500 vào 2020. Gần gũi hơn chúng ta có những con chip di động vẫn có hiệu năng cao như Apple dòng A hay Snapdragon, Tegra thế hệ 32-bit trở về sau. Tuy vậy cái giá để có hiệu năng cao cũng không khác x86 là bao - hao điện và toả nhiều nhiệt. Những thứ tưởng chừng là trò đùa cho smartphone như quạt tản nhiệt bỗng trở thành một sản phẩm tiêu dùng đàng hoàng. Cũng vì thế mà ARM buộc phải cho ra kiến trúc big.LITTLE để tối ưu việc khi nào thì cần tiết kiệm pin mà khi nào thì cần hiệu năng cao.

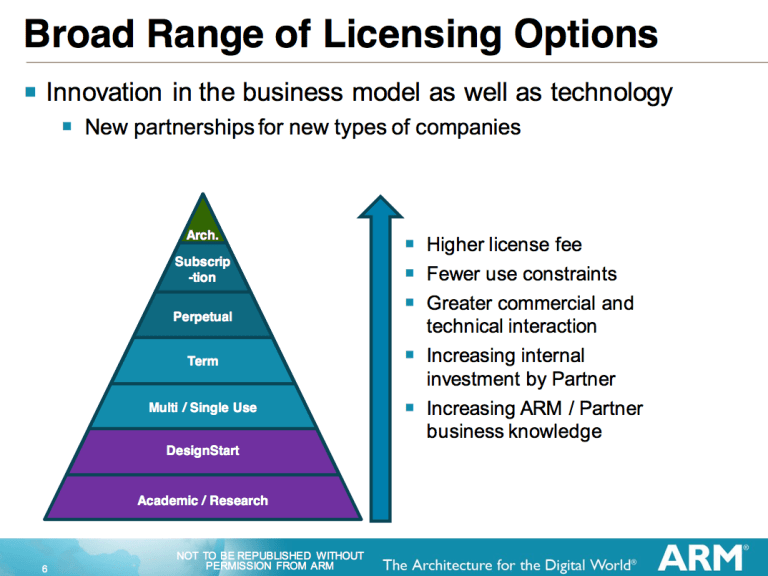

Cơ chế cho thuê bản quyền kiến trúc của ARM khác việc đóng kiến trúc x86 của Intel

Nhưng trong khi ARM với nhiều hãng phát triển (do cơ chế cấp phép bản quyền) dần tốt hơn theo năm tháng thì x86 với chỉ 2 đại diện Intel và AMD (vẫn có VIA nhưng đừng tính làm gì) có vẻ không thay đổi nhiều, mà cụ thể nhất là Intel. Mình có từng phân tích tại sao Intel lại như thế ở một bài viết trước. Có thể gom chung tất cả vào một câu - lãnh đạo như shit! Vì cơ bản người đứng đầu không ra gì thì sản phẩm khó mà tiến bộ được. Nhưng đó là tình hình trước khi Pat Gelsinger về cầm trịch Intel (tương tự AMD là con thuyền đang đắm trước khi Lisa Su làm CEO). Có thể thấy mọi thứ thay đổi đã bắt đầu từ Ice Lake (ICL), cho tới Meteor Lake (MTL) và nay là LNL. Dĩ nhiên LNL không phải điểm đến cuối cùng, chúng ta vẫn còn Arrow Lake (ARL) và Panther Lake, nhưng đó là ở thì tương lai.

Sự tiến bộ của x86 (CISC) và ARM (RISC)

Có thể đôi khi bạn thắc mắc - cái gì làm nên sức mạnh của một con chip? Silicon, dĩ nhiên! Mọi con chip mạnh nhất hiện nay đều có số lượng transistor tới hàng chục, thậm chí hàng trăm tỷ. Nhưng đây cũng là một cách nhìn rập khuôn. Silicon về cơ bản giống như số tiền bạn có trong tay, còn làm sao để số tiền đó sinh lời một cách nhanh chóng, an toàn và hiệu quả thì lại tuỳ thuộc nhiều yếu tố. Với chip mà nói, đó là kiến trúc của nó. Hiện tại, có nhiều loại mô hình kiến trúc khác nhau. Nhưng phần lớn tồn tại chủ yếu là RISC và CISC.

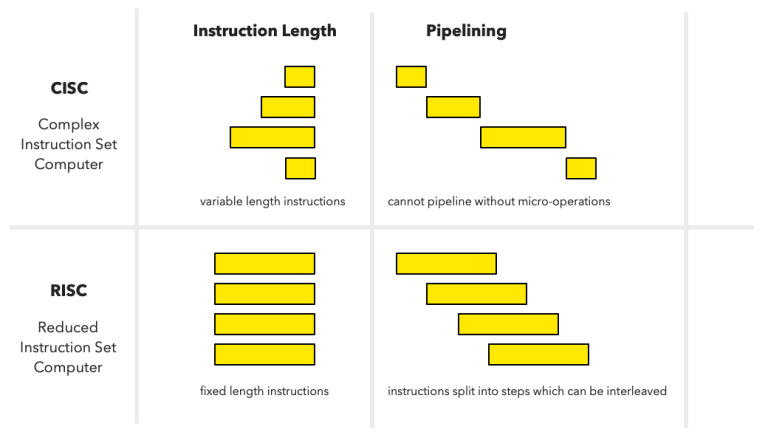

Khác biệt chính giữa CISC vs. RISC là chiều dài tập lệnh

Có điều RISC vs. CISC là một chủ đề khá dông dài, mình sẽ không nói nhiều ở đây. Chúng ta chỉ tập trung vào các khác biệt chính và những gì dẫn tới kiến trúc LNL của hôm nay. RISC về cơ bản là kiến trúc chip trong đó các tập lệnh có cấu trúc được rút gọn, chiều dài cố định, thường chỉ được thực thi bên trong các ALU/FPU, chúng không truy cập vào dữ liệu ở bộ nhớ ngoài mà chỉ xử lý trên các thanh ghi (register). RISC có những tập lệnh riêng để thực hiện chức năng lấy dữ liệu ở ngoài vào. Vì thế nó còn được gọi là kiến trúc xuất-nhập (load-store).

CISC ngược lại, sử dụng các tập lệnh cấu trúc phức tạp hơn, thường có cả chức năng truy cập dữ liệu ngoài thanh ghi (ví dụ cache hoặc DRAM). Mục đích là cho phép chúng có thể thực hiện được nhiều phép toán chỉ với 1 tập lệnh (1 tập lệnh RISC thường chỉ làm được 1 việc). Vì vậy, tập lệnh CISC có chiều dài biến động chứ không cố định như RISC. Chi tiết này dẫn tới việc thiết kế ống lệnh (pipeline) cho CISC phức tạp hơn cũng như làm sao để mở rộng số ống lệnh CISC khó hơn RISC nhiều.

Thiết kế ống lệnh cho CISC phức tạp hơn RISC

Nhưng nói vậy không nghĩa RISC luôn luôn đơn giản. Khi chiều dài các thanh ghi tăng lên thì chiều dài các tập lệnh cũng phải tăng. Đồng thời để có thể giải quyết được nhiều công việc hơn thì RISC cũng cần phải có nhiều tập lệnh hơn trước đó. Ngoài ra vì chiều dài tập lệnh cố định (ở 1 thế hệ kiến trúc), khi chuyển giao sang thế hệ kế tiếp sẽ đòi hỏi việc bổ sung thêm cơ chế chia chiều dài để có thể xử lý được tập lệnh cũ. Bản thân CISC không gặp trục trặc này vì với chiều dài biến động, mọi tập lệnh cũ đều vẫn chạy bình thường trên kiến trúc mới.

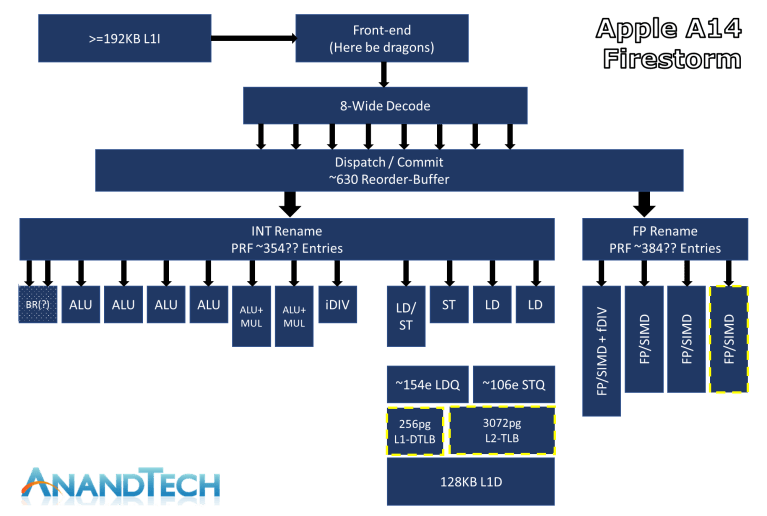

Nói chung, khác biệt chủ đạo giữa thiết kế chip RISC và CISC chủ yếu nằm ở cách làm sao xử lý các tập lệnh. Một cách thuần tuý thì hệ số IPC càng cao (số tập lệnh chạy được trên 1 chu kỳ) thì kiến trúc đó càng mạnh. RISC do đặc trưng tập lệnh đơn giản, việc mở rộng số ống lệnh tương đối dễ dàng hơn CISC. Cho tới hiện tại, các chip dòng M của Apple có số decoder vào khoảng 8/10-wide, Snapdragon X Elite của Qualcomm là 8-wide decoder, Zen 4 của AMD là 4-wide decoder, Sunny Cove/Cypress Cove là 5-wide decoder.

RISC cần thực thi nhiều tập lệnh hơn để xử lý 1 công việc

Lẽ tất nhiên con số decoder của từng hãng không nói lên chúng hơn/kém hãng khác. Mà là cơ sở để đánh giá sự thay đổi kiến trúc trong nội bộ hãng đó. Lấy ví dụ kiến trúc K7/K8/K10 của AMD đều là 3-wide decoder, còn Zen 1/2/3/4 cùng 4-wide decoder, nhưng chênh lệch IPC giữa từng kiến trúc là có khác biệt. Còn với Intel, kể từ thế hệ Core đầu tiên cho tới Skylake (Core đời 6-10) là 4-wide, duy nhất đời 11 (Cypress Cove) là 5-wide. 6-wide decoder xuất hiện từ đời 12 và duy trì tới tận hôm nay. Vậy còn LNL?

8-wide decoder.

Bức tốc chóng mặt

Một chuyện rõ ràng là kích thước decoder chỉ là một phần trong tổng thể kiến trúc con chip. Nó không phải thang đo tuyệt đối về sức mạnh (IPC). Song nó cho thấy "tiềm năng" của con chip này đến mức nào. Một cách ví von dễ hiểu về kiến trúc chip là một doanh nghiệp sản xuất, với một nhân xử lý là một nhà máy. Trong đó decoder là bộ phân chuyên trách nhận đơn hàng từ ban giám đốc/đối tác gửi xuống. Decoder có kích thước càng lớn thì càng phân tích được rõ đơn hàng hơn cũng như chia được nhiều đầu việc hơn cho các phân xưởng/dây chuyền ở dưới.

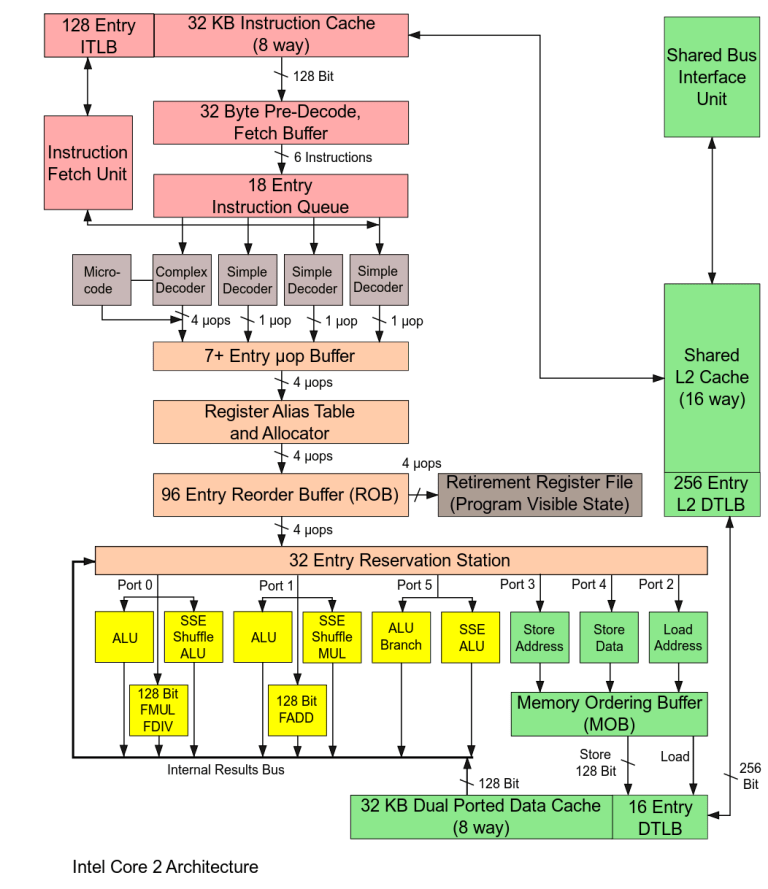

Kiến trúc Intel Core (2006) với 4-wide decoder

Và một logic rất cơ bản là không ai tuyển tới 8 ông trưởng phòng kinh doanh nhưng chỉ tuyển 1 trưởng phòng sản xuất. Cần có sự cân bằng giữa bộ phận chia đầu việc bộ phận xử lý công việc. Trên thực tế bao lâu nay, decoder là bộ phận có số lượng thấp hơn các đơn vị còn lại. Như đã nêu ở trên, AMD duy trì 3-wide decoder trong rất nhiều năm liền rồi mới lên 4-wide. Intel cũng không khác. Nhưng ở lần ra mắt LNL này (chính xác là P-core Lion Cove), thay vì phát triển tiếp 6-wide decoder có trên Redwood Cove (MTL), Intel đã lên thẳng 8-wide! Tại sao phải gấp gáp đến vậy?

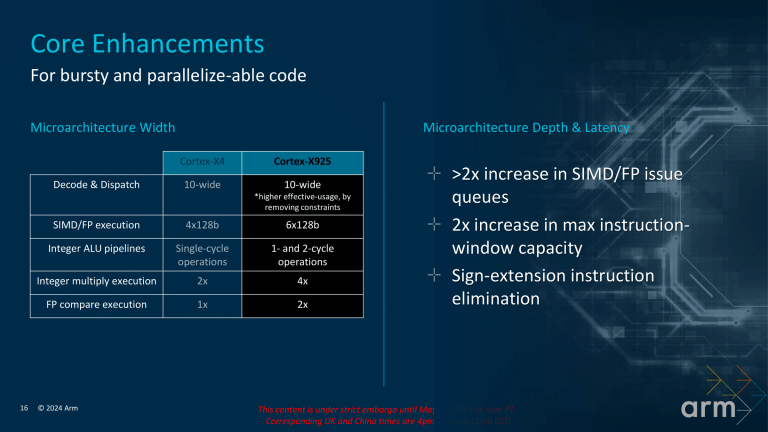

Kiến trúc ARM Cortex-X925 (2024) với 10-wide decoder

Apple đã áp dụng 8-wide decoder từ 2020

Vì phe ARM đã lên đến 8/10-wide decoder. Cách đây không lâu, ARM vừa công bố nhân Cortex-X925 mới, có thể xem là bản nâng cấp từ Cortex-X4 ra mắt trong 2023. Trong đó cả 2 nhân Cortex này đều là 10-wide decoder. Mặc dù decoder của x86 và ARM khác nhau, nhưng quả thực cứ duy trì số lượng decoder thấp thì quả có nhiều khó khăn để so găng với đối thủ. Thế nên Intel chọn cách "nhảy cóc" lên thẳng 8-wide để không bị tụt hậu. Và theo kinh nghiệm của mình, Lion Cove sẽ là nền móng cho kiến trúc x86 của Intel trong nhiều năm tới (vì thay đổi số lượng decoder gần như tương đương với một kiến trúc mới hoàn toàn - một kiến trúc thường tồn tại 4-5 năm).

P-core Lion Cove - Go big or go home

Bắt đầu từ Alder Lake, Intel áp dụng kiến trúc hybrid tương tự big.LITTLE của ARM. Tương tự, LNL cũng sẽ có 2 loại nhân x86 P-core Lion Cove và E-core Skymont. Trong đó, Lion Cove như đã nói, chính là "trái tim" sức mạnh của toàn bộ con chip (tương tự Zen 5 bên AMD).

Front-end

Phần đầu tiên trong một kiến trúc chip luôn là front-end, nơi nhập các yêu cầu công việc từ OS gửi xuống. Trên Lion Cove, khu vực này được mở rộng đáng kể. BPU hay bộ phận tiên đoán rẽ nhánh, có chức năng "đoán trước" các tập lệnh sẽ được dùng ở các chu kỳ sau, được mở rộng gấp 8 lần thế hệ trước! Vai trò của BPU tương tự như thư ký, hỗ trợ decoder sắp xếp công việc cho các thành phần execution. Sự mở rộng này cho thấy Intel muốn tối đa hoá số lượng tập lệnh có thể xử lý được.

Hỗ trợ thêm cho decoder là các µQueue và µCache. Trên các vi xử lý hiện đại, tập lệnh không được xử lý ngay tại chỗ mà sẽ bị chia nhỏ thành vi lệnh (micro-ops). Mục đích là để đơn giản hoá quá trình execution ở dưới. Đây cũng là điểm mà ranh giới của CISC và RISC trở nên nhạt nhoà - chúng chủ yếu chỉ khác biệt ở phần front-end nơi các tập lệnh có chiều dài khác nhau, còn khi chuyển thành vi lệnh thì "con anh con tôi" cũng thế. µCache của Lion Cove tăng lên 12-wide, tăng gấp 1,5 lần 8-wide của Redwood Cove. Kích thước µQueue cũng tăng lên, có điều Intel không nêu cụ thể là bao nhiêu.

Out-of-order (OoO) engine

Lion Cove là một kiến trúc hoàn toàn mới và khu vực OoO thể hiện rõ điều đó. Thành phần Retire được tách ra hẳn khỏi nhóm Allocate/Rename/Ellimation/Zero Idiom. Lý do chủ yếu vì Retire cần được tăng kích thước nhiều hơn, lên tới 12-wide. Nhóm Allocate cũng tăng 8-wide, gần như là tương ứng với kích thước 8-wide của decoder. Đáng chú ý hơn, thanh ghi Scheduler nay được chia tách ra Integer riêng và Vector (floating-point) riêng, cho thấy sự chuyên môn hoá vai trò.

Số lượng cửa sổ tập lệnh cũng được tăng từ 512 lên 576 đơn vị. Số cổng xử lý cũng tăng từ 12 lên 18 cổng. Trong đó 4 cổng dùng cho FPU (Vector), 6 cổng cho INT, 8 cổng dùng cho phân loại xử lý địa chỉ dữ liệu (AGU).

Execution

So với các kiến trúc trước, Lion Cove có khác biệt đáng kể khi đưa FPU ra riêng khỏi INT. Nếu như trước đây FPU dùng chung cổng với INT để nhận công việc từ front-end/OoO thì nay nó đã đứng độc lập. Theo quan điểm cá nhân, mình cho rằng Pat Gelsinger đang muốn đưa Intel trở lại đường đua siêu máy tính (HPC), nơi mà AMD đang rất có ưu thế. Vả chăng mà nói, Pat cũng là một trong các cựu kỹ sư đã từng tham gia thiết kế Itanium - một trong những dự án rất tham vọng của công ty này.

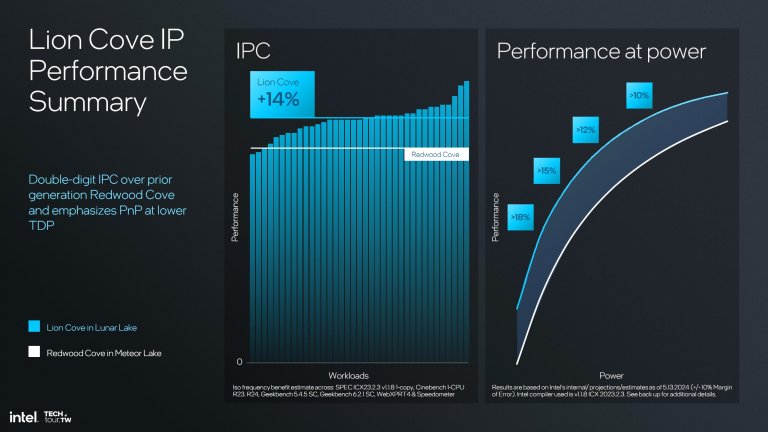

Và Pat không chỉ làm mỗi việc tách đôi 2 FPU và INT, ông còn tăng năng lực xử lý của từng cụm. So với Redwood Cove, các thành phần cụm INT Lion Cove đều tăng 1 đơn vị (6 ALU, 3 JUMP, 3 SHIFT), riêng MUL tăng gấp 3 lần. FPU Lion Cove cũng được "độ thêm" sức mạnh với 4 ALU (tăng từ 3) và 2 FP Divider (tăng từ 1). Nhìn chung, năng lực xử lý của Lion Cove mạnh hơn Redwood Cove và rất mạnh so với Cypress Cove (hiện dùng trên Core đời 14).

Back-end

Tất nhiên các thay đổi ở phía trên sẽ vô nghĩa nếu Lion Cove không có sự cải tiến nào về bộ nhớ. Quay lại ví dụ nhà máy, nếu front-end đại diện cho ban giám đốc gửi công việc xuống, OoO là phòng quản lý sản xuất, execution là các dây chuyền nhà máy thì back-end chính là bộ phận lưu kho (nội bộ xưởng - kho tổng nằm ở ngoài hay DRAM). Nhà máy mở rộng sản xuất thì nội bộ kho cũng phải tăng cường thêm, nếu không hàng hoá làm ra sẽ bị dồn ứ - thiệt hại sản lượng.

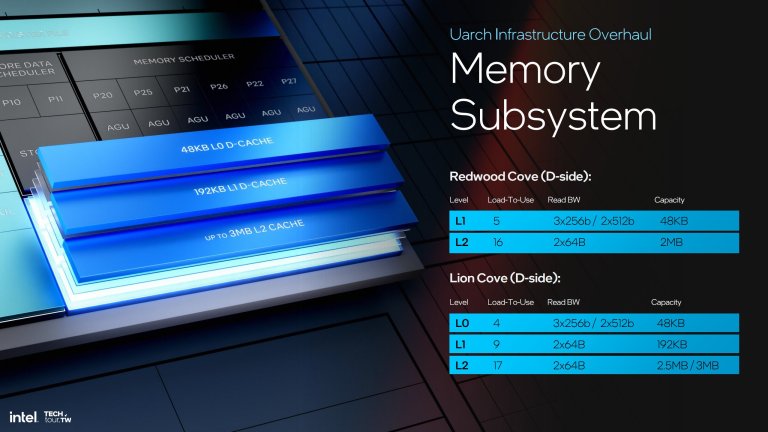

Trên Lion Cove, một chi tiết thú vị là sự xuất hiện của L0 Cache. Xét về thông số thì nó không khác L1 Cache trên Redwood Cove là bao (48 KB), ngoại trừ độ trễ giảm từ 5 xuống 4 chu kỳ. Lion Cove vẫn có L1 Cache nhưng dung lượng cao hơn (192 KB) và độ trễ cũng nhiều hơn (9 chu kỳ). Còn L2 Cache có độ trễ tăng nhẹ từ 16 lên 17 chu kỳ, song dung lượng tăng lên đáng kể tới 2.5/3 MB (3 MB có lẽ là bản server).

Tổng quan lại, phần back-end của Lion Cove "rộng rãi" hơn rất nhiều, âu cũng là để chứa được nhiều dữ liệu hơn trước. Intel cho biết về tổng thể, Lion Cove có mức IPC tăng 14% so với Redwood Cove.

6 thoughts on “Phân tích kiến trúc CPU Intel Lunar Lake - Tỉnh giấc sau đêm dài (P1)”