Intel Panther Lake technical analysis: CPU, SoC and 18A

Details on the Intel 18A process technology along with the CPU and SoC used for Panther Lake – the next generation mobile processor.

Panther Lake represents a significant step forward in Intel's product roadmap, not only in terms of innovation but also in terms of balancing performance and energy efficiency on mobile PC platforms. The design philosophy of Panther Lake is to take the efficient architecture of Lunar Lake and scale it to a larger scale while delivering higher performance. A key contributor to this design philosophy is the Intel 18A process . Intel built Panther Lake with three ambitions:

- Increased architectural flexibility, aiming to expand the ability to meet diverse market needs, from thin, light, energy-efficient devices to high-performance devices for creators and gamers.

- Scale performance across all tasks, focusing on increasing performance not only for CPU, but also for graphics and artificial intelligence, responding to the task trends on modern PCs.

- Leading in energy efficiency, setting a new standard for performance per watt, inheriting and promoting what Lunar Lake achieved before.

With Panther Lake, Intel not only pushes performance but also focuses on optimizing performance at every level, from the microarchitecture of the processor core to the power management of the entire SoC.

Article content

Panther Lake Platform

Intel 18A Process

All of Panther Lake's performance and energy efficiency gains are thanks to the Intel 18A process technology. More than just a die-size reduction, Intel 18A represents a leap forward in Intel's semiconductor manufacturing technology, integrating two groundbreaking technologies: RibbonFET and PowerVia.

When switching to the Intel 18A process, Intel faced many complex technical challenges. Intel CPU architects had to rebuild the entire design platform, from logic libraries, memory arrays, custom circuits to temperature sensors. In particular, by moving the power grid to the back of the wafer, PowerVia technology completely changed the design rules. Thanks to PowerVia, the entire space on the front of the wafer was dedicated to signal routing. The two main benefits of PowerVia are higher transistor density and a more powerful power system with less voltage drop because more resources can be devoted to power delivery without competing with signal lines.

Removing the front-panel grid means losing the natural signal shielding, which is crucial for protecting high-frequency signals (e.g., operating frequency) from crosstalk. To address this, engineers must employ new techniques in physical design, such as adjusting the width and spacing of signal paths to ensure signal integrity.

Intel Tech Tour 2025: The 18A era, reshaping AI strategy

Essence from Lunar Lake and Arrow Lake

Intel did not build Panther Lake from scratch, but it is the result of a synthesis and development process, combining the best points from Lunar Lake and Arrow Lake. For Lunar Lake , Panther Lake inherits the legacy of energy efficiency on the x86 platform (x86 power efficiency). Lunar Lake has brought a completely new experience of energy efficiency, or in other words, battery life, for x86 processors. To achieve that, Lunar Lake owns the Efficiency Cluster design and Memory-Side Cache. Panther Lake has taken these concepts, upgraded with new generation cores and integrated them as the foundation for energy efficiency.

Arrow Lake brings a lesson in performance scaling to Panther Lake. Arrow Lake focuses on increasing core count and multi-threaded performance. Panther Lake has applied this philosophy by providing configurations up to 16 CPU cores, combining the power of both P-core and E-core on the same compute cluster to meet heavy multi-threaded tasks.

By combining two distinct design philosophies from Lunar Lake and Arrow Lake, Panther Lake aims to create a comprehensive mobile processor that is both performance-oriented and energy-efficient. Panther Lake is capable of operating efficiently at low power levels for everyday tasks, while also being able to unleash powerful multi-threading and graphics power when needed. This approach allows Intel to create a single platform that can scale to serve many different market segments, simply by changing the configuration of module components.

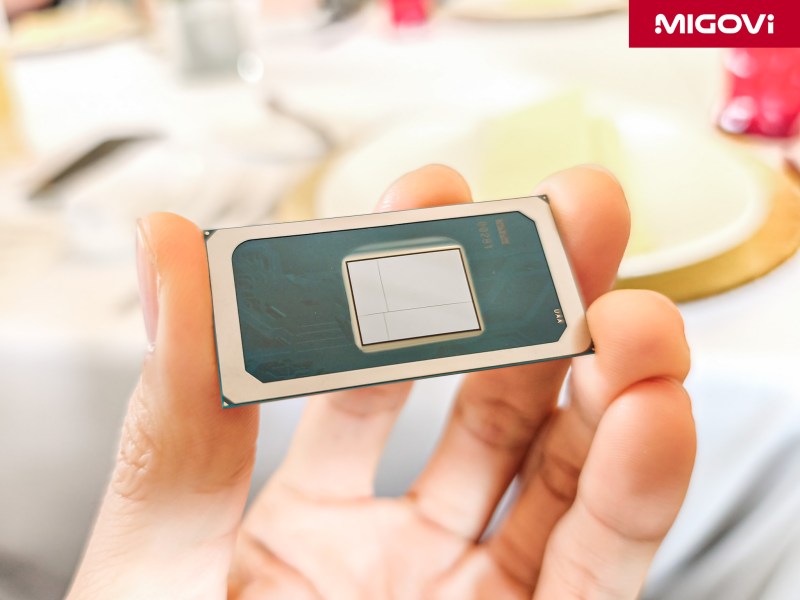

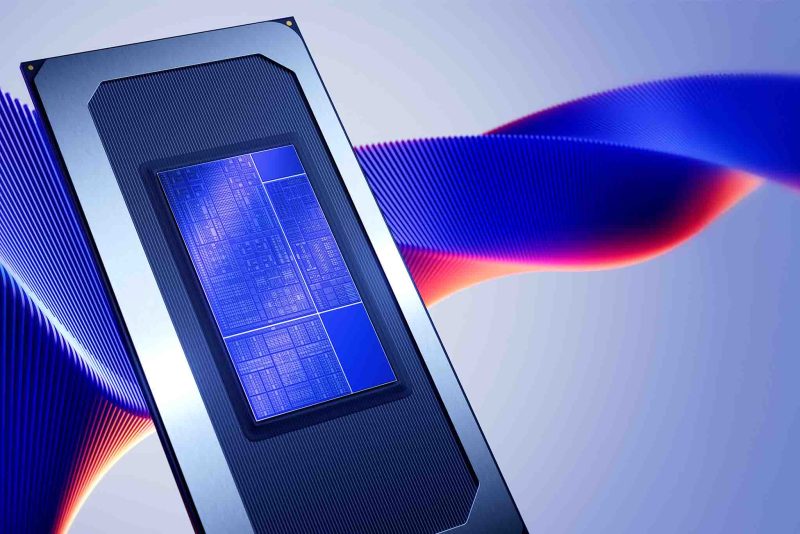

Modular SoC design

Panther Lake represents the semiconductor industry’s shift to modular design, also known as tile-based architecture. Instead of a single monolithic die, Panther Lake is made up of multiple specialized “tiles,” each performing a separate function and connected together using advanced packaging and interconnect technologies.

3-Tile Structure

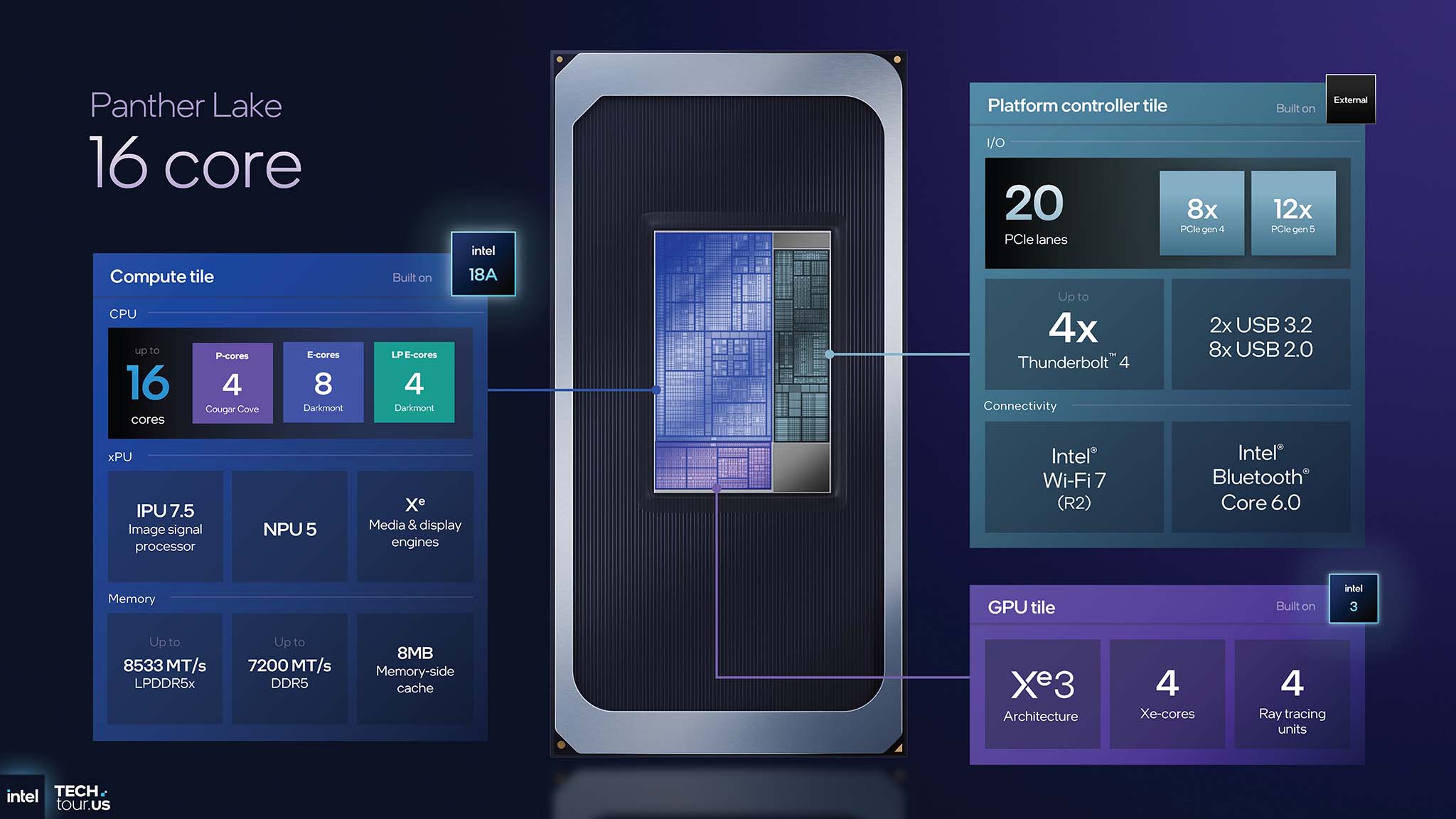

Panther Lake is built from 3 main tiles, assembled on a passive base die using Foveros packaging technology. First, the Compute Tile is the heart of the SoC, containing most of the main computing tools. The Compute Tile is manufactured on the Intel 18A process, including CPU cores (P-core Cougar Cove and E-core Darkmont), IPU 7.5 (Imaging Processing Unit), Media & Display Engine (multimedia and display tools) and memory subsystem. Intel concentrates the core computing components into a single tile on the most advanced process to optimize performance and energy efficiency.

Next, the GPU Tile is where the graphics engine is located, based on the new Xe3 architecture. The GPU Tile is now completely separate from the Compute Tile, manufactured on the Intel 3 process. By separating it from the Compute Tile, Intel can easily and independently expand the graphics capabilities of the chip. This helps meet the needs of many customer segments without having to redesign the entire SoC.

Finally, the Platform Controller Tile, similar to Lunar Lake, consolidates all I/O, connectivity and security functions. The Platform Controller Tile includes PCIe, Thunderbolt, USB, Wi-Fi 7, Bluetooth controllers and other platform functions. Intel groups the I/O IPs into a single tile, simplifying the Compute Tile design and allowing the Platform Controller Tile design to be reused across multiple products.

Foveros and Scalable Fabric Gen 2

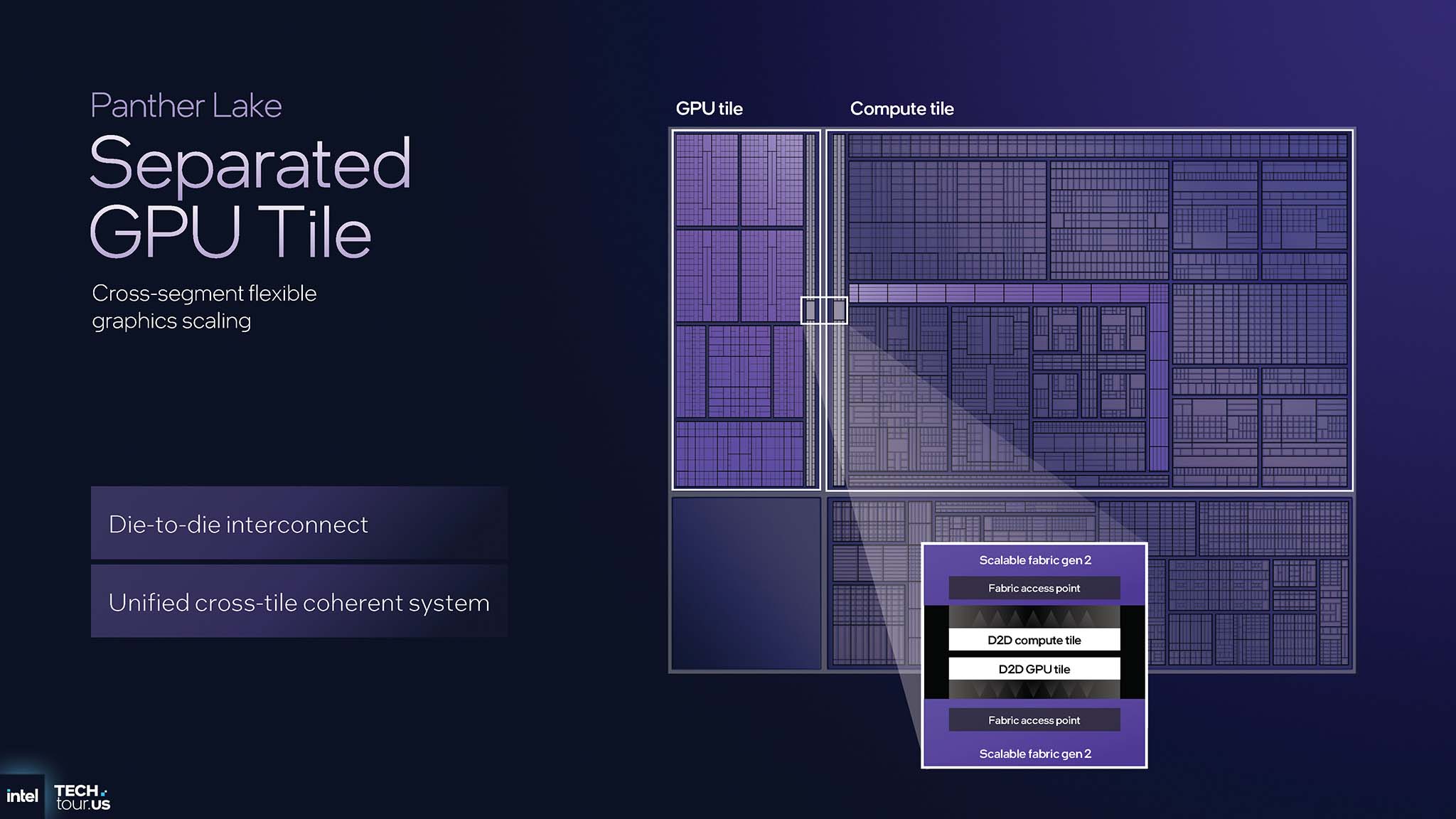

There are two foundational technologies used in Panther Lake to interconnect tiles into a system: Foveros and Scalable Fabric Gen 2. Panther Lake uses the mature Foveros-S (or Foveros 2.5D) packaging technology to assemble tiles onto a passive substrate. Foveros-S enables high-density die-to-die connectivity, ensuring high bandwidth and low latency between dies, which is extremely important for maintaining system performance.

Meanwhile, Scalable Fabric Gen 2 can be understood as a kind of digital glue, helping to connect everything together. Initially, Scalable Fabric was developed for Arrow Lake and the second generation on Panther Lake helps to increase scalability. Scalable Fabric Gen 2 supports multiple physical layers (multi-physical layer support), deployed on Foveros die-to-die connections. Scalable Fabric Gen 2 is also not dependent on partitions (Partitioning-agnostic), instead using a unified transactional protocol layer, which can operate within a tile or between different tiles. This ability makes separating functions into different tiles easy and seamless. In addition, Scalable Fabric Gen 2 is also not dependent on IP (IP-agnostic), can carry many different functional protocols. This allows for the integration of diverse IP without changing the fabric.

Intel has a collection of pre-designed tiles with different functions, based on the combination of Foveros and Scalable Fabric Gen 2, which can flexibly choose tiles, then assemble them into different SoCs, creating a powerful modular platform. It can be seen that designing and manufacturing tile-based semiconductors is similar to playing with LEGO blocks.

Separate GPU Tile

The most important scalability change in Panther Lake is the separation of the GPU Tile from the Compute Tile. Thanks to the flexibility of Scalable Fabric Gen 2, this separation is simple to implement, using an efficient die-to-die connection to communicate between the two tiles, making them act as if they were part of a unified system. By creating a modular GPU Tile, Intel can address different market segments and price points more efficiently. Instead of incurring the huge cost of designing and validating multiple large monolithic SoCs with different GPU configurations, Intel can now combine the same Compute Tile with GPU Tiles of different sizes. Panther Lake is the most obvious example: there are two configurations using a 4-core Xe3 GPU Tile, while the top-end configuration uses a 12-core Xe3 GPU Tile, all in the same package size.

This chiplet approach offers maximum flexibility. Intel can quickly create different SKUs to meet market demand. Yield management is also better because smaller dies (like GPU Tiles) have better yield ratios than large monolithic dies. If a GPU Tile fails, just scrap that tile instead of the entire expensive SoC. Additionally, products using the tile-based approach also have faster time to market.

Platform configuration and extensibility

Panther Lake, with its modular design, becomes a scalable product line that meets a variety of form factors and thermal envelope requirements. It is worth noting that all configurations that Panther Lake offers are implemented on a single package design, thereby providing maximum flexibility for OEMs in designing suitable products.

3 Panther Lake configurations

Intel announced three main configurations for Panther Lake, targeting different performance segments. All three configurations share the NPU 5, IPU 7.5, Media & Display Engine along with modern connectivity such as Wi-Fi 7 and Thunderbolt 4.

8-core configuration (Basic): provides balanced mobile performance, suitable for common tasks. Including:

- CPU: Total 8 cores, including 1 performance cluster with 4 P-cores (Cougar Cove) and 1 energy efficiency cluster with 4 LP E-cores (Darkmont).

- GPU: Xe3 architecture with 4 Xe cores and 4 Ray Tracing units.

- Memory: Supports LPDDR5x up to 6800 MT/s and DDR5 up to 6400 MT/s.

- I/O: 12 PCIe lanes (4x Gen5, 8x Gen4).

- Cache: 8 MB Memory-Side Cache.

16-core configuration (High performance): for heavy multi-threaded computing tasks. Including:

- CPU: Upgrade to a total of 16 cores (excluding LP E-cores), including a performance cluster with 4 P-cores (Cougar Cove) and 8 E-cores (Darkmont), plus a 4 LP E-core energy efficiency cluster.

- GPU: Keeps Xe3 architecture with 4 Xe cores and 4 Ray Tracing units.

- Memory: Increased bandwidth, supporting LPDDR5x up to 8533 MT/s and DDR5 up to 7200 MT/s.

- I/O: Significantly expands to 20 PCIe lanes (12x Gen5, 8x Gen4), ideal for high-performance devices.

- Cache: Keep 8 MB Memory-Side Cache.

16-core 12Xe configuration (Graphics performance): this is the highest-end configuration, optimized for gaming, content creation and intensive AI tasks. Including:

- CPU: Keep the powerful 16-core configuration (4 P-core + 8 E-core) plus 4 LP E-core.

- GPU: The GPU Tile expands to 12 Xe cores and 12 Ray Tracing units, 3x the graphics computing power compared to the other two configurations, delivering discrete class performance.

- Memory: Optimized for maximum bandwidth, supporting LPDDR5x up to 9600 MT/s (providing approximately 150 GBps bandwidth). This configuration does not support DDR5 SO-DIMM.

- I/O: Back to 12 PCIe lanes (4x Gen5, 8x Gen4), same as base configuration.

- Cache: Still retains 8 MB Memory-Side Cache.

Flexible for OEM

Previously, Lunar Lake had a highly integrated design with a dedicated PMIC (Power Management IC) and on-package memory. With Panther Lake, Intel offers platform design options to OEMs. In terms of power delivery, Panther Lake allows for the use of a discrete VR (Voltage Regulator) topology. This gives OEMs the freedom to design a power supply system that can deliver higher currents to meet the performance needs of compute engines in high-performance platforms, instead of being limited by a fixed PMIC.

Panther Lake memory is also flexible, with support for both LPDDR5x (soldered on the motherboard) and DDR5 SO-DIMM (upgradable modules). OEMs can prioritize thin, light, power-efficient designs with LPDDR5x, or prioritize upgradeability, high capacity and lower cost with DDR5 SO-DIMM. This flexibility allows OEMs to create more diverse products that suit a wide range of price points and end-user needs. This approach allows OEMs to leverage existing board designs and have more flexibility in component selection. This results in better pricing for the end product (due to cost savings), while also expanding Panther Lake's reach across the entire mobile market.

Cougar Cove and Darkmont microarchitecture

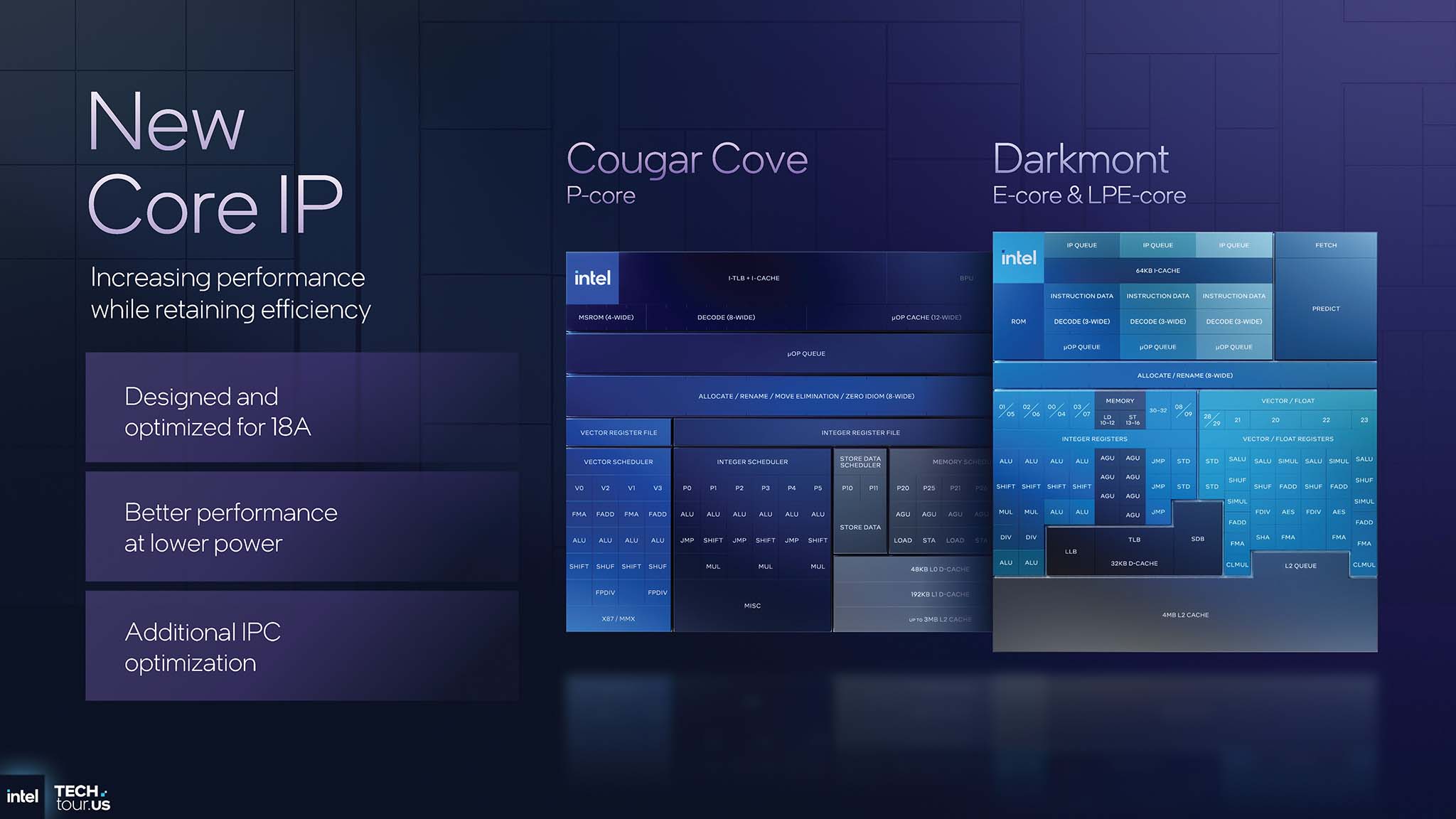

At the core of any processor is the CPU core architecture. In Panther Lake, Intel uses two new core microarchitectures, Cougar Cove (P-core) and Darkmont (E-core). Both microarchitectures are specifically designed and optimized for the Intel 18A process. The new microarchitecture promises better performance at lower power and optimized IPC (Instructions Per Cycle).

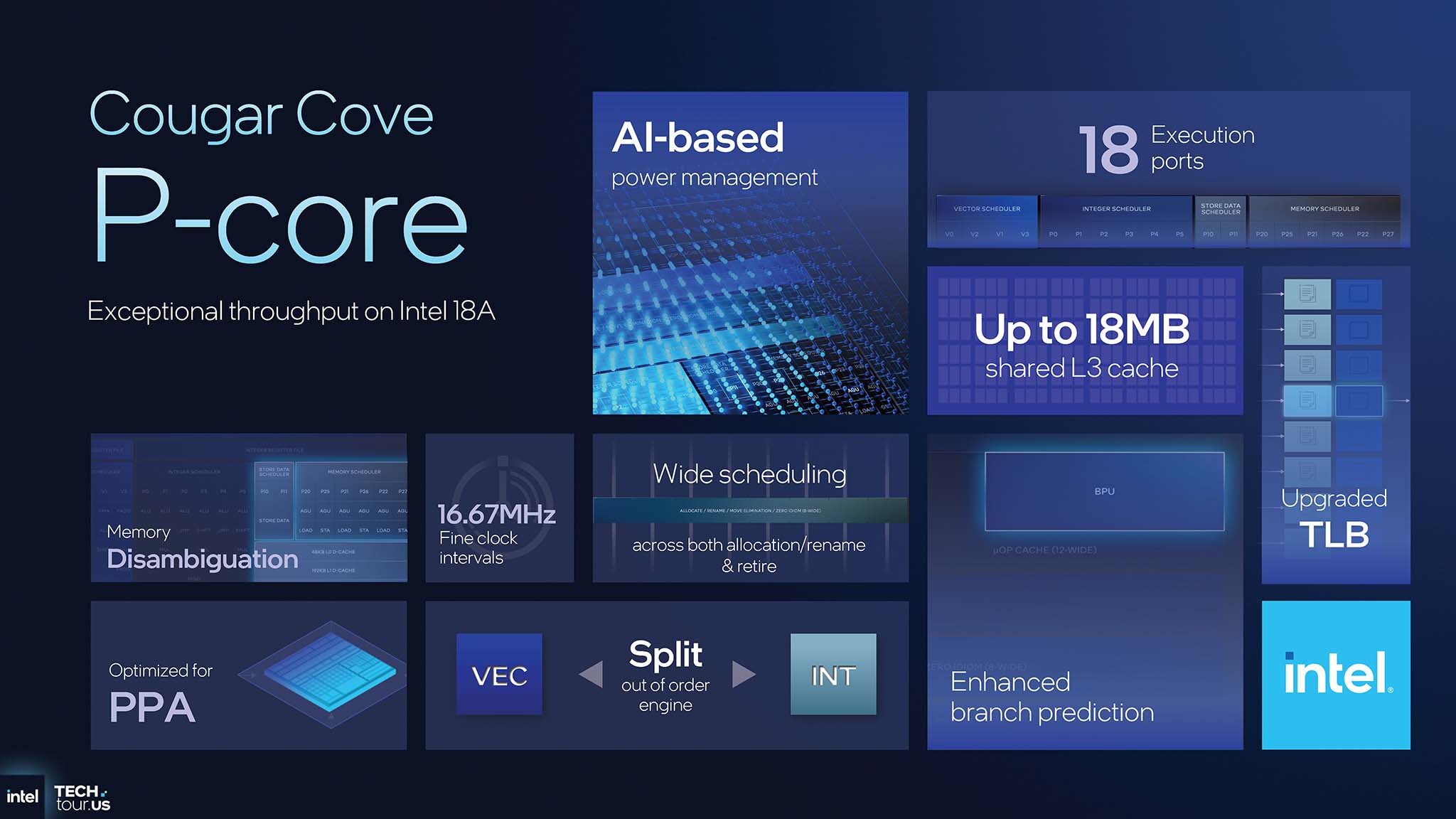

P-Core Cougar Cove

The next generation P-Core featured in Panther Lake is Cougar Cove, optimized for the Intel 18A process. Cougar Cove focuses on refining and improving the existing mechanisms of Lion Cove (on Arrow Lake and Lunar Lake) to deliver higher performance.

Cougar Cove's first optimization is Memory Disambiguation, a major improvement in the management of memory load and store instructions. Cougar Cove improves the processor's ability to predict when a load and store instruction are related. When predictions are accurate, the processor can schedule load instructions more accurately, avoiding unnecessary conflicts. The result is increased IPC and more stable, reliable performance.

The next improvement is the TLB (Translation Lookaside Buffer). This is a buffer used to speed up the process of translating virtual addresses to physical addresses. As tasks become more complex, TLB capacity becomes an important factor. The 18A process allows engineers to increase the TLB capacity by 1.5 times compared to the previous generation. This helps reduce the number of TLB misses, making complex applications run faster and smoother.

Another important optimization is Brand Prediction, which has been continuously improved in every CPU generation. The previous microarchitecture – Lion Cove – introduced a new BPU (Brand Prediction Unit) algorithm and Cougar Cove took lessons from Lion Cove’s post-silicon process to refine and perfect it. The BPU algorithm on Cougar Cove improves prediction accuracy. In addition, it increases the capacity, expanding the size of multi-level prediction structures. This reduces prediction latency, as predictions can be found in closer, faster BPU cache levels. Metadata is also enhanced, expanding the depth of prediction bits (such as the probability of a branch being taken). Brand Prediction optimizations result in shorter prediction latency, higher prediction bandwidth and better prediction accuracy. Optimizing BPU not only increases performance (less time wasted on wrong predictions) but also saves energy (less useless work is done).

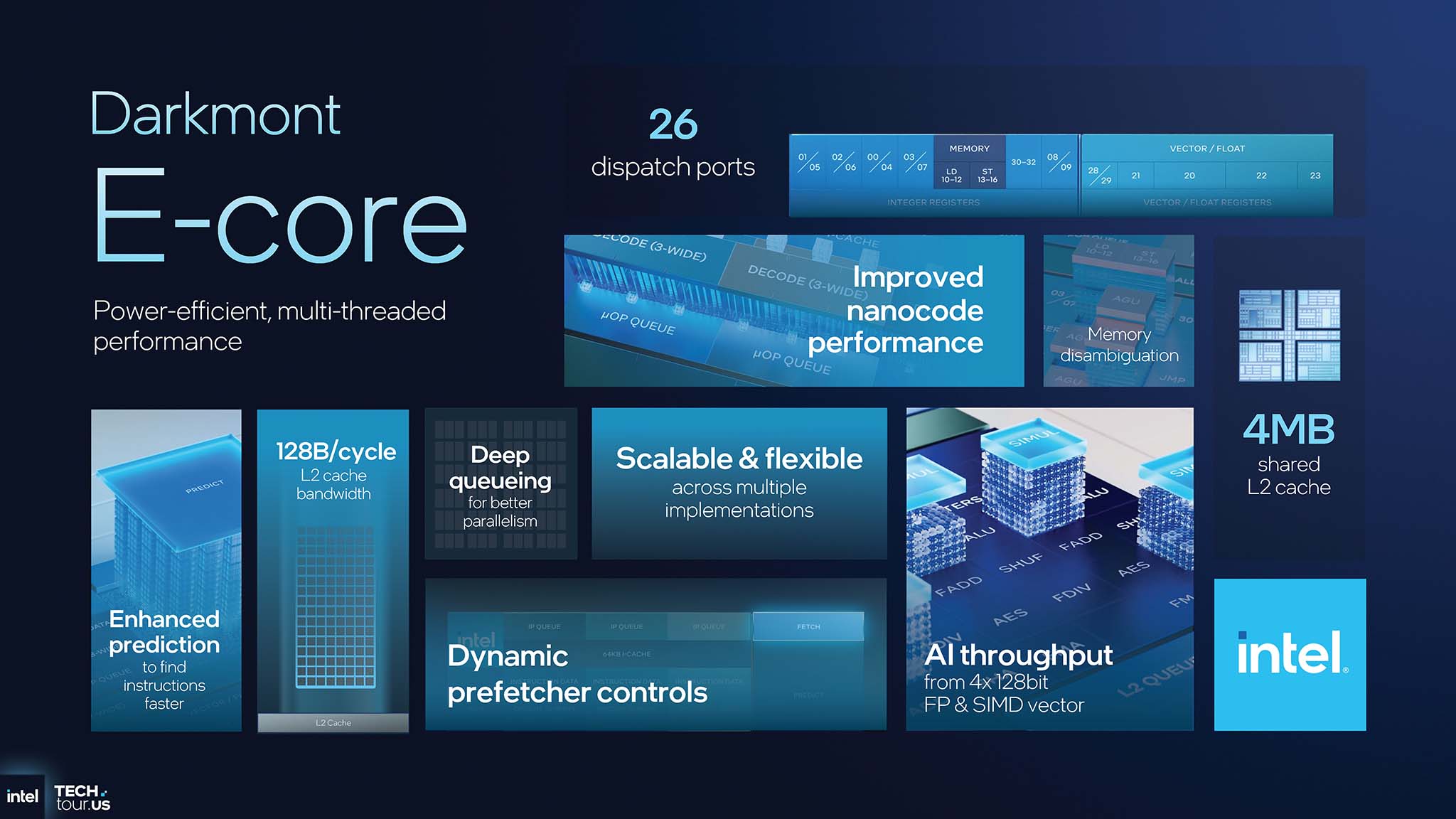

E-Core Darkmont

Darkmont is a new generation E-Core, inheriting the foundation of the previous Skymont, optimized for multi-threaded performance and high energy efficiency. Like Cougar Cove, Darkmont focuses on fine-tuning smart mechanisms to improve performance. Darkmont also has improvements in branch prediction, the algorithm has been fine-tuned for more accuracy. A notable feature is loop stream detection, which allows the processor to turn off the front-end when executing small loops, thereby saving significant energy.

Darkmont has Dynamic Prefetcher Controls. Prefetcher is a mechanism to predict and pre-load data from memory into cache. Darkmont uses a dynamic prefetcher system, based on real-time telemetry data to decide the aggressiveness of prefetching. When a task needs a lot of data, the prefetcher will work more aggressively and vice versa. This helps the system react more flexibly to changes in task types.

Nanocode is a unique feature of Intel’s E-core, essentially a way to execute complex x86 instructions (which require many micro-ops) using dedicated hardware right on the front-end, instead of relying on a traditional microcode sequencer. This allows for parallel and out-of-order execution of micro-op sequences, saving latency, bandwidth and die area. Darkmont expands the number and optimizations that can be handled by nanocode, allowing for increased performance for complex instructions.

Similar to P-Core, the E-Core design team also implemented Memory Disambiguation technology. Sharing technology and solving similar problems between P-Core and E-Core helps improve performance across the entire hybrid architecture.

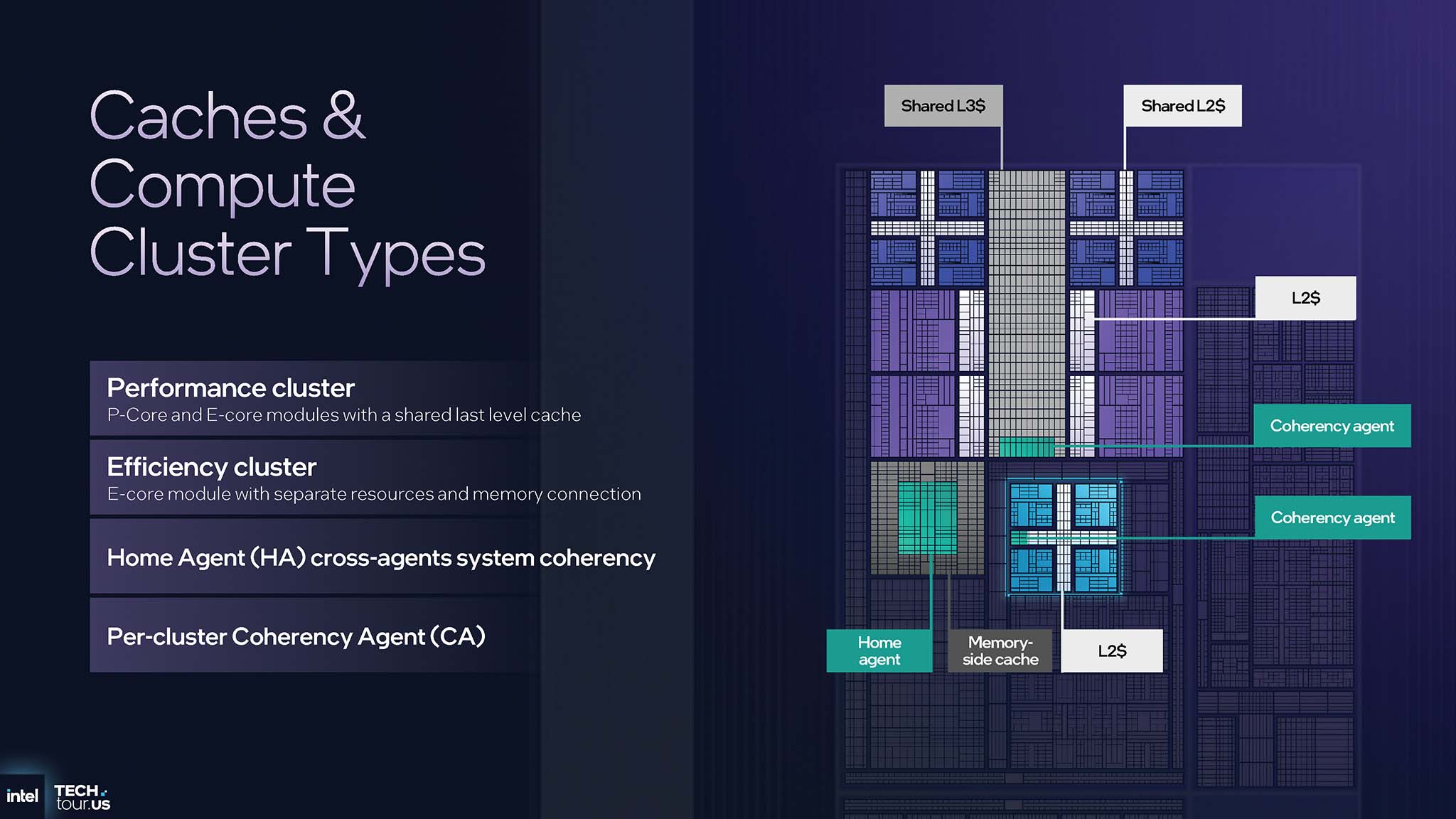

Compute Clusters and Caching

The Performance Cluster contains P-Cores and E-Cores located on the Compute Tile. The cores in this cluster are connected via a high-bandwidth fabric and share a common Last Level Cache (L3). Sharing the L3 cache optimizes bandwidth and latency, allowing the cores to communicate and share data efficiently, which is especially important for complex multi-threaded tasks.

The Efficiency Cluster, also known as Panther Lake's Low Power Island, consists of a 4-core LPE-core (Darkmont) module with a shared 4 MB L2 cache. The Efficiency Cluster has a dedicated power supply and power management system, connected directly to the memory subsystem. This is a major upgrade over Arrow Lake's Low Power Island and leverages the successful Lunar Lake design, allowing it to handle a wide range of tasks from background services to mid-range computing while maintaining extremely low power consumption.

Panther Lake inherits the 8MB physical cache that first appeared on Lunar Lake, also known as Memory-Side Cache. The role of this cache is extremely important for system efficiency. Memory-Side Cache acts as an L4 cache, helping to take full advantage of the Efficiency Cluster performance by improving latency and bandwidth, thereby increasing the core IPC. More importantly, Memory-Side Cache significantly reduces DRAM traffic, resulting in reduced power consumption. The saved energy can be used to increase core clock speeds. In addition, it serves as an efficient cache for other engines such as the NPU or Media Engine, which is especially valuable in low-power scenarios.

For Panther Lake, E-cores are no longer just E-cores. Panther Lake has E-cores in the Compute Tile for multi-threaded throughput and LPE-cores in the Efficiency Cluster for sustained performance and battery life. The entire system is designed to intelligently divide workloads into three distinct compute domains (LPE-cores, Compute E-cores and P-cores), each with its own cache and power optimizations. The complexity of Panther Lake’s design is also why Intel Thread Director is so important.

Accelerator IP

In the AI PC era, SoC performance is not only about the power of the CPU core, but also about specialized accelerators, from graphics, AI to image processing.

Xe3 GPU

Panther Lake features the new Xe3 graphics architecture, which is scalable to increase performance without compromising energy efficiency. On the highest configuration Panther Lake, Intel can scale the Xe3 GPU to 12 Xe cores and 12 Ray Tracing units. The L2 cache has a capacity of up to 16 MB, increasing bandwidth and reducing memory access latency. In terms of AI performance, Panther Lake's GPU is capable of AI computations of up to 120 TOPS, ready to meet AI inference needs in addition to graphics processing.

NPU 5

The Neural Processing Unit – NPU 5 – is designed to deliver high performance on a small die area and low power consumption. This allows for optimized AI inference tasks to run continuously on the client. NPU 5 offers over 40% improvement in TOPS per unit area (TOPS/area) compared to the Lunar Lake NPU. The computational power is also significant with 3.8 times higher performance than the Arrow Lake-H NPU. The peak performance of NPU 5 reaches 50 TOPS, allowing for processing of complex AI models directly on the device without a network connection. In addition, NPU 5 adds support for the FP8 format, which, although less accurate, is more energy and bandwidth efficient for many AI models.

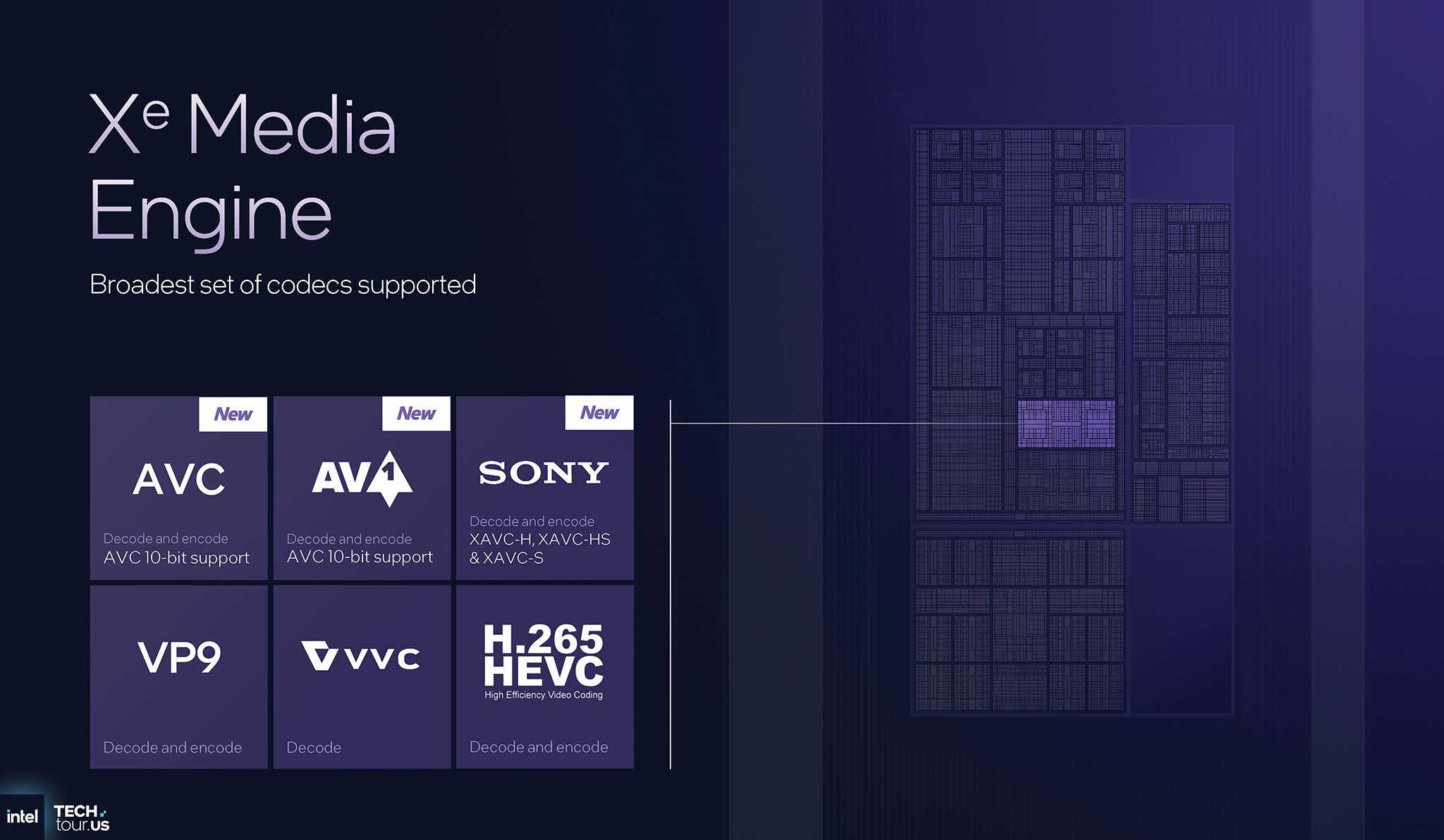

IPU 7.5 and Media Engine

The IPU 7.5 (Image Processing Unit) delivers crystal-clear images and videos. The IPU 7.5 integrates AI-based algorithms for noise reduction and local tone mapping, resulting in clean, clear images with better contrast and brightness. In addition, the IPU 7.5 also supports hardware-accelerated Staggered HDR technology, allowing for wide dynamic range photography. More importantly, the use of hardware reduces power consumption by up to 1.5W compared to software processing – an extremely important factor for battery-powered devices.

Panther Lake's Media Engine has been expanded to support new codecs, meeting the needs of professionals and content creators. The Media Engine adds AV1 4:4:4 encoding and decoding, improving quality for screen-sharing applications. 10-bit AVC – a popular format in professional cameras – is also supported.

Smart software and energy management

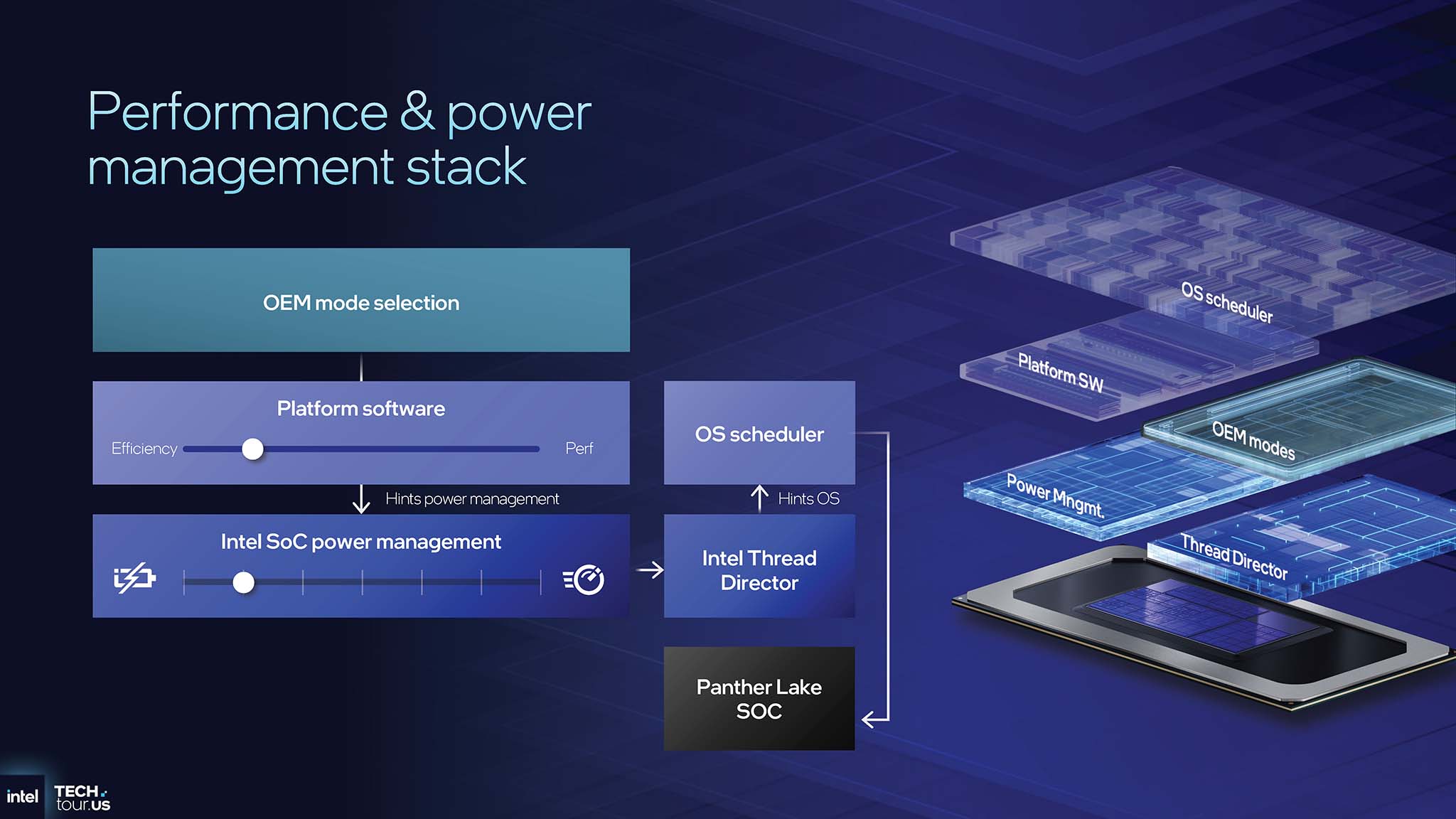

Half of the Panther Lake story is hardware, the other half is software that unlocks the full potential of the complex hybrid architecture. As mentioned, the complexity of Panther Lake's design necessitates advanced scheduling and intelligent power management.

Intel Thread Director

Intel Thread Director is a platform technology that allows the operating system to understand the performance and efficiency differences between P-Core and E-Core. Thread Director works by using telemetry data in the hardware to classify the work threads. This information is then provided to the operating system scheduler via the Hardware Feedback Interface table, helping the operating system make smarter decisions about which threads to put on which cores.

The introduction of the Cougar Cove and Darkmont microarchitectures has resulted in performance differences (delta IPC) between core types. The Thread Director classification models have been retrained to accurately reflect these changes, ensuring optimal instruction delivery to the operating system. The models have also been trained with real-world usage scenarios that reflect how users multitask, rather than just single benchmarks.

The system can now receive feedback from the P-core, Compute E-core and LPE-core, providing a more comprehensive view of the state of the entire SoC. Power and performance decisions are moved from software directly to the SoC. This change allows for tighter control and faster response to changes in workload and temperature conditions. Additionally, improved telemetry allows for a more consistent experience in performance and energy efficiency when the user switches between AC (plug-in mode) and DC (battery mode).

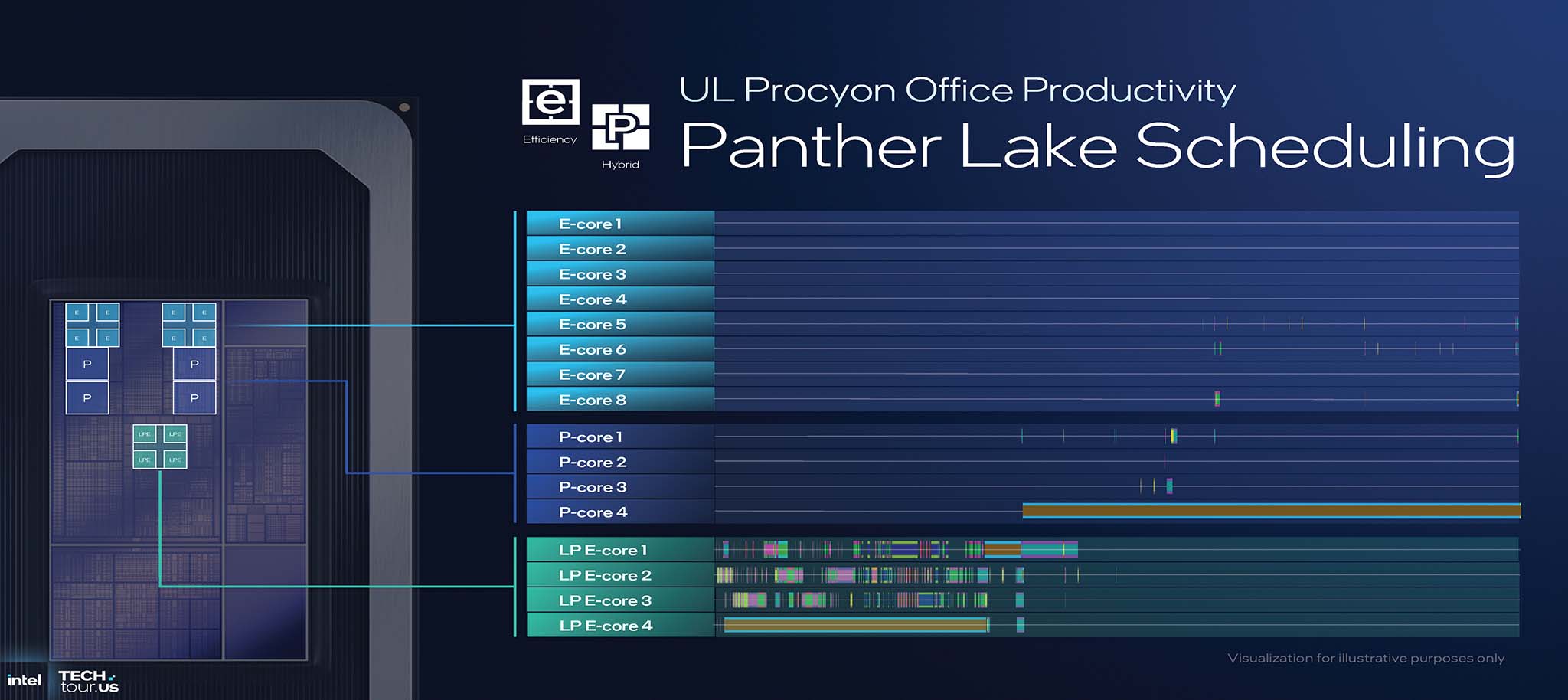

Scheduling with OS Containment Zones

Scheduling has improved over the generations. While Raptor Lake prioritized P-cores, Meteor Lake and Lunar Lake prioritized E-cores, Panther Lake flexibly combines the two. Panther Lake interacts with Windows' Containment Zones. Containment Zones allow the operating system to group cores with similar characteristics together and apply different scheduling methods. There are 3 Containment Zones:

- Efficiency Zone: Contains LPE cores in the Low Power Island. Light, background tasks are prioritized in this zone to maximize battery life. For example, during a Teams video call, the LPE cores have enough power to handle the work, keeping the performance cluster in a deep sleep state.

- Hybrid/Compute Zone: Includes all cores on the Compute Tile (both P-cores and E-cores). When a task exceeds the capacity of the Efficiency Zone, it will be moved to this zone. Depending on the rules (e.g., game optimization), the operating system can prioritize starting on the E-cores of this zone to save power for the GPU, or start on the P-core for the fastest response.

- Zoneless: In heavily multi-threaded tasks like Cinebench, the system will ignore zones and mobilize all available cores (LPE-core, E-core, P-core) to achieve maximum throughput.

Intel Thread Director, when combined with the operating system's Containment Zones, creates a multi-layered and intelligent scheduling system. Thanks to that, Panther Lake is able to adapt to all types of tasks, optimizing both performance and energy efficiency.

Intel Intelligent Experience Optimizer

One of the most notable software innovations on Panther Lake is Intel Intelligent Experience Optimizer. This technology solves a problem inherent in PCs: users often have to manually switch between power modes provided by the operating system (High performance, Balanced, Power saver). Intelligent Experience Optimizer is a combination of Intel Dynamic Tuning software and firmware optimizations, acting as an “automatic transmission” for the PC.

When the user is in “Balanced” mode, the system automatically and dynamically switches between “performance gear” and “efficiency gear” based on the workload in real time. The decision to switch is based entirely on workload analysis, without the need to identify the specific application. When the system detects a high performance need (e.g., rendering video), it automatically switches to a higher “gear”. When the workload becomes lighter, it returns to a lower “gear” to save energy.

The Intel Intelligent Experience Optimizer delivers significant benefits. In Intel’s internal tests, it increased performance by up to 19-20% in tasks like Procyon Office Productivity and Cinebench without user intervention. The Intel Intelligent Experience Optimizer also helps close the performance gap between AC and DC modes. This tool helps Intel ensure that end users truly experience the improvements from the hardware, following the “it just works” philosophy, realizing the AI PC era.

3 thoughts on “Intel Panther Lake technical analysis: CPU, SoC and 18A”