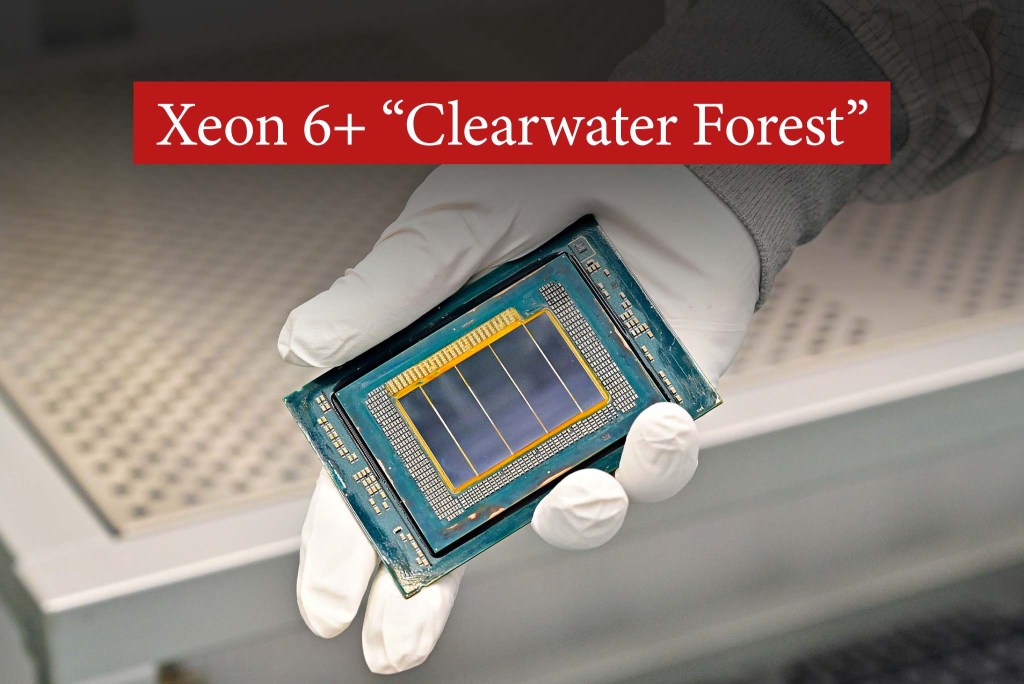

Intel Xeon 6+ “Clearwater Forest” – Bước nhảy vọt với Intel 18A và Darkmont

Clearwater Forest hay Xeon 6+ xuất hiện tại Intel Tech Tour 2025, cho thấy bước nhảy vọt với Intel 18A và Darkmont E-core.

Nội dung bài viết

Intel và tầm nhìn cho trung tâm dữ liệu

Lãnh đạo và định hướng mới

Intel Tech Tour 2025 đánh dấu thời điểm quan trọng đối với mảng DCG (Data Center Group) của Intel, từ khía cạnh công nghệ tới thông điệp chiến lược mà ban lãnh đạo mới truyền tải. Ông Kevork Kechichian, Phó Chủ tịch Điều hành và Tổng Giám đốc mới của DCG, thẳng thắn thừa nhận những thách thức trong quá khứ của tập đoàn. Ông nhấn mạnh rằng những vấn đề về sự chậm trễ trong lộ trình sản phẩm và khả năng cạnh tranh không phải là “vấn đề R&D” mà là “vấn đề lãnh đạo“. Đáng chú ý ở chỗ Kevork chỉ mới là lãnh đạo ở Intel được 18 ngày (tại thời điểm Intel Tech Tour 2025). Phát biểu thẳng thắn của ông cho thấy sự thay đổi văn hóa sâu sắc, hướng tới sự minh bạch và trách nhiệm giải trình cao hơn đối với những người quan tâm Intel (nhà đầu tư, truyền thông, nhân viên, khách hàng…).

Không chỉ thừa nhận sự yếu kém, Kevork Kechichian còn đưa ra 3 giá trị cốt lõi sẽ định hình tương lai của DCG: lắng nghe khách hàng, cung cấp sản phẩm cạnh tranh, thực thi đúng hẹn với chất lượng cao. Đây là những nguyên tắc kinh doanh cơ bản, tuy nhiên khi chúng được nhấn mạnh trong bối cảnh hiện tại, chúng ta có thể thấy nỗ lực của Intel nhằm tái thiết lập niềm tin với khách hàng, đối tác sau thời gian dài nhiều hoài nghi. Ông Kechichian cũng chia sẻ rằng ông nhiều lần từ chối các lời mời của Intel trước đây, lý do là không thể tin tưởng vào ban lãnh đạo cũ. Quyết định gia nhập ở thời điểm này cho thấy niềm tin vào tầm nhìn và khả năng thực thi của đội ngũ lãnh đạo mới, với Lip-Bu Tan dẫn đầu. Rõ ràng các vấn đề của Intel không nằm ở việc thiếu hụt tài năng – đội ngũ kỹ sư – mà là định hướng chiến lược và khả năng ra quyết định của cấp cao nhất.

Tư duy “Fabless” trong IDM

Ông Kechichian đề cập tới việc áp dụng tư duy của 1 công ty fabless ngay trong lòng 1 nhà sản xuất thiết bị tích hợp (IDM – Integrated Device Manufacturer) hàng đầu như Intel. Kevork đã có kinh nghiệm dày dặn tại các công ty fabless như Qualcomm và Arm, nhờ đó nhận ra rằng sự tiện lợi của việc sở hữu nhà máy (fab) ngay kế bênh có thể vô tình tạo ra sự thiếu kỷ luật trong quy trình thiết kế. Một ví dụ dễ hình dung là dựa dẫm quá nhiều lần vào quy trình “tape-out” để sửa lỗi, thay vì tối ưu chính xác từ đầu.

Chiến lược mới yêu cầu đội ngũ R&D của Intel phải hoạt động với sự nghiêm ngặt của 1 công ty fabless, vốn phải đảm bảo thiết kế chính xác ngay từ lần đầu tiên để tránh các chi phí sản xuất khổng lồ. Khi kỷ luật thiết kế này được thiết lập, việc sở hữu các nhà máy tiên tiến nhất sẽ không còn là sự tiện lợi mà trở thành một hệ số nhân (multiplier) thực sự – lợi thế cạnh tranh chiến lược. Sự kết hợp giữa thiết kế tối ưu và quy trình sản xuất hàng đầu sẽ cho phép Intel tạo ra các sản phẩm vượt trội về hiệu năng và hiệu quả năng lượng.

Tư duy “fabless” ngay trong IDM sẽ là cơ chế phòng thủ chống lại sự tự mãn, đồng thời là nền tảng cốt lõi cho sự thành công của mô hình kinh doanh dịch vụ gia công bán dẫn của Intel (Intel Foundry Services – IFS). Khi đội ngũ thiết kế nội bộ của Intel – khách hàng lớn nhất và khắt khe nhất của chính các nhà máy Intel – hoạt động với kỷ luật cao nhất, họ sẽ thúc đẩy các nhà máy phải cung cấp bộ công cụ thiết kế quy trình (Process Design Kit – PDK) cùng các công cụ hỗ trợ tốt nhất. Điều này sẽ làm cho năng lực sản xuất của Intel trở nên hấp dẫn hơn đối với các khách hàng fabless bên ngoài. Về cơ bản, Intel đang sử dụng chính các sản phẩm tiên tiến nhất của mình, như Xeon 6+, để tôi luyện và hoàn thiện quy trình làm việc giữa khâu thiết kế và sản xuất, tạo ra một vòng lặp tích cực giúp cả 2 mảng kinh doanh cùng phát triển.

Lộ trình Xeon 6

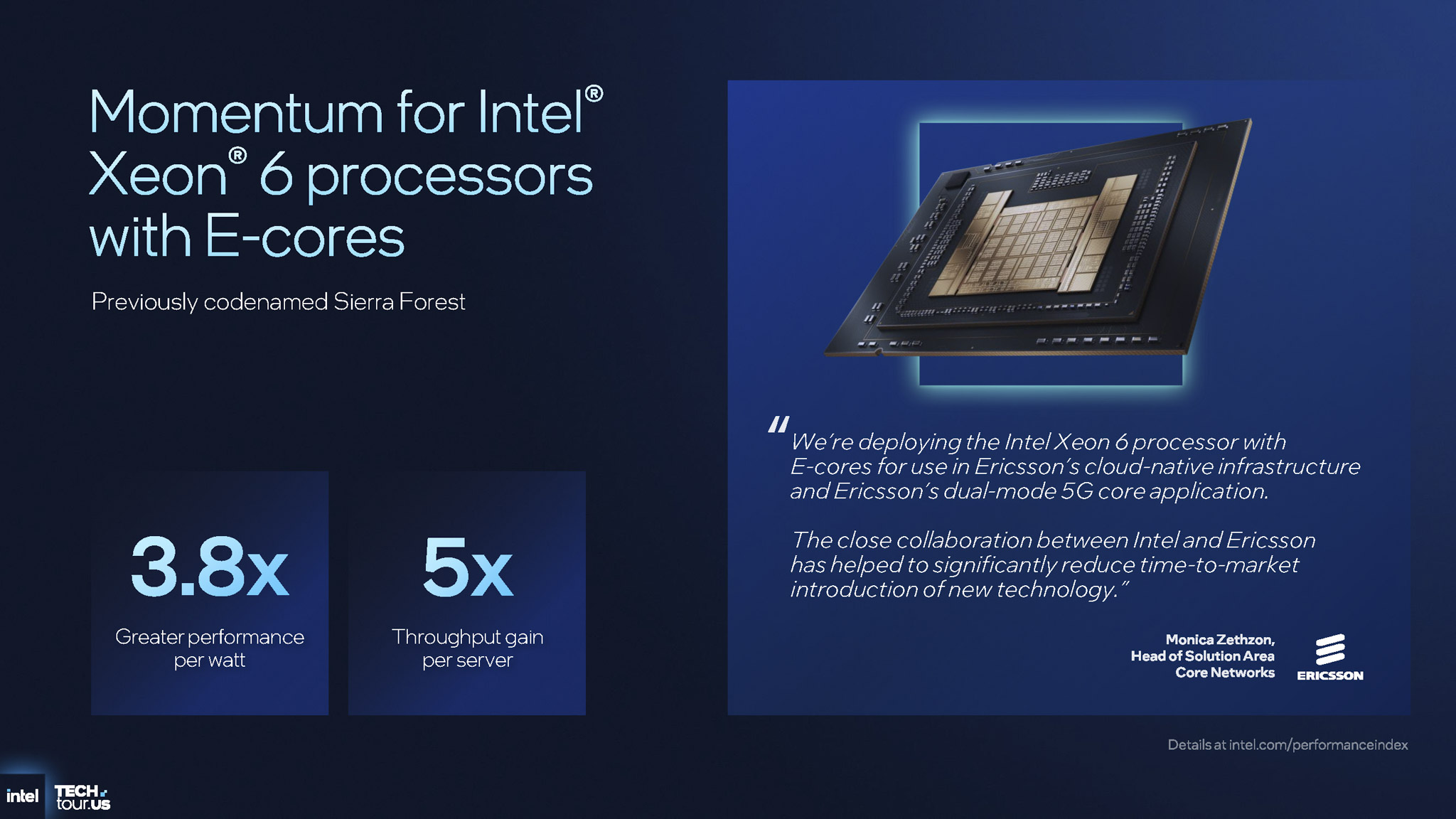

Các trung tâm dữ liệu hiện đại có nhu cầu đa dạng, do đó Intel cung cấp chiến lược vi kiến trúc kép cho dòng sản phẩm Xeon 6. Ra mắt từ năm 2024, Xeon 6 Series gồm 2 nhánh riêng biệt, tối ưu hóa cho các loại tải công việc khác nhau. Intel Xeon 6 với P-core (Granite Rapids) được thiết kế cho các tải công việc chuyên sâu về tính toán (compute-intensive workloads) như HPC và AI, tập trung vào hiệu năng trên mỗi nhân. Trong khi đó Intel Xeon 6 với E-core (Sierra Forest) tập trung vào hiệu năng trên mỗi watt điện, phục vụ nhu cầu tải công việc cần mật độ cao (high-density compute), cũng như khả năng mở rộng theo chiều ngang (scale-out workloads), điển hình như như điện toán đám mây (cloud-native), vi dịch vụ (microservices) và mạng viễn thông (telco).

Không có 1 kiến trúc CPU nào có thể tối ưu cho tất cả các kịch bản sử dụng, bằng chứng là Xeon 6 với 2 nhánh riêng biệt. Thay vì tạo ra con chip “một kích cỡ cho tất cả”, Intel đang phân khúc thị trường rõ ràng. Dòng P-core sẽ cạnh tranh trực tiếp với các CPU x86 hiệu năng cao của đối thủ, trong khi dòng E-core là câu trả lời trước các CPU dựa trên kiến trúc ARM trong không gian đám mây và viễn thông, nơi mật độ nhân và tổng chi phí sở hữu (TCO) là những yếu tố hàng đầu.

Trong bối cảnh lúc bấy giờ, việc ra mắt Xeon 6 với E-core (Sierra Forest) có thể được xem là bước đi phòng thủ chiến lược, giúp Intel có sản phẩm cạnh tranh để giữ chân khách hàng trong phân khúc đang bị các đối thủ ARM tấn công. Sierra Forest có những thành công ban đầu với các đối tác lớn như Ericsson, sau đó là HPE, Nokia, phoenixNAP. Tuy nhiên, sự ra đời của Intel Xeon 6+ (Clearwater Forest) mới thực sự là đòn tấn công của Intel. Với việc gấp đôi số nhân, ứng dụng tiến trình Intel 18A và vi kiến trúc Darkmont, Clearwater Forest không chỉ là sản phẩm “đủ tốt” mà được thiết kế để dẫn đầu thị trường về mật độ và hiệu quả.

Nền tảng Intel Xeon 6+

Clearwater Forest

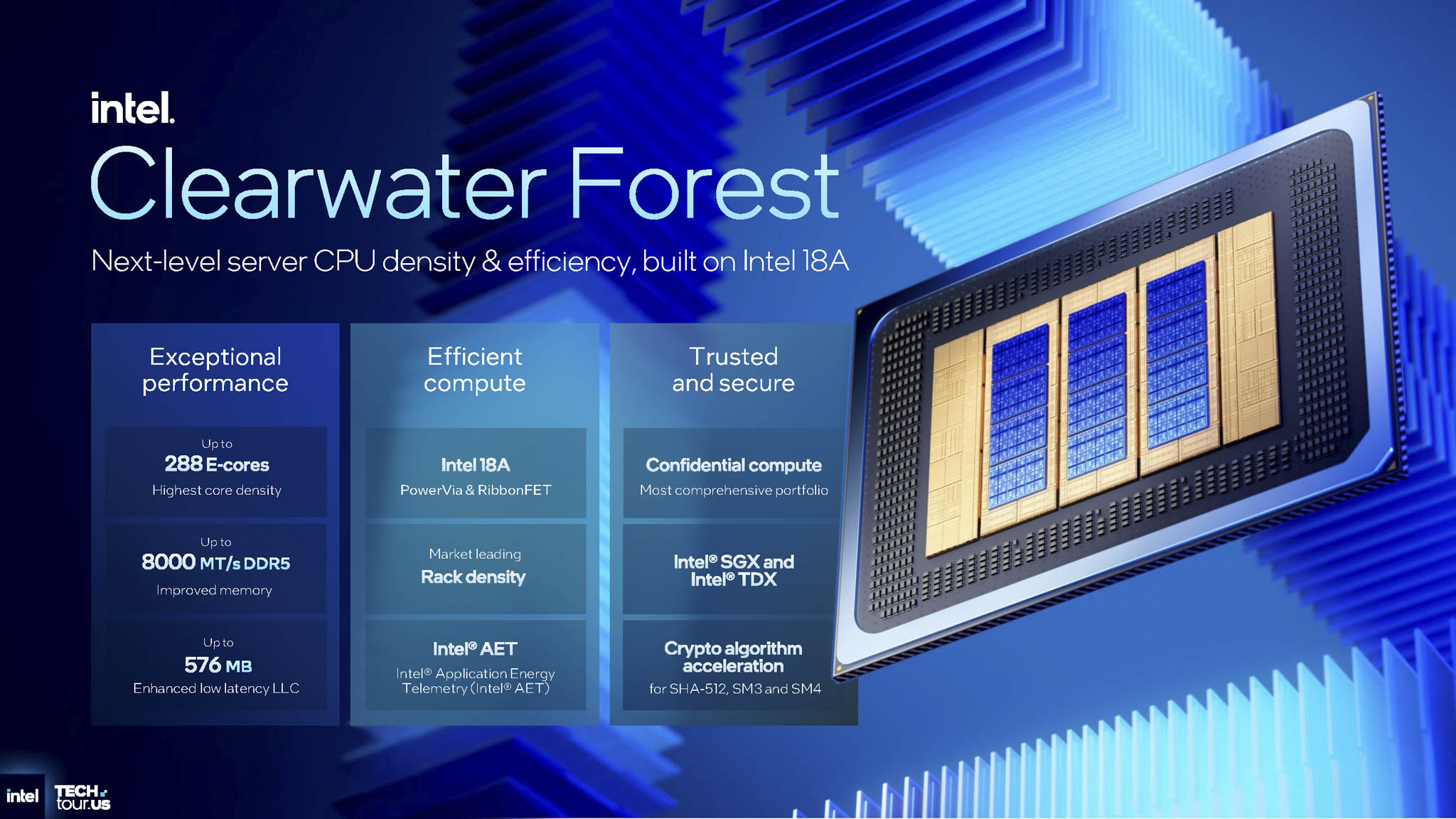

Intel Xeon 6+ với tên mã Clearwater Forest là CPU 18A đầu tiên dành cho trung tâm dữ liệu, trang bị E-core. Dấu “+” trong tên gọi không chỉ cho thấy cải tiến mới mà còn là bước nhảy vọt đáng kể so với nền tảng Xeon 6 hiện tại. Clearwater Forest là sản phẩm tiên phong, tích hợp hàng loạt công nghệ hiện đại của Intel trên 1 con chip duy nhất.

Intel Xeon 6+ cung cấp tới 288 nhân E-core với vi kiến trúc Darkmont, hỗ trợ bộ nhớ DDR5 với tốc độ lên đến 8000 MT/s, trang bị bộ đệm cấp cuối (Last Level Cache – LLC) khổng lồ lên tới 576 MB. Quan trọng hơn cả, đây là bộ xử lý trung tâm dữ liệu đầu tiên của Intel được chế tạo trên tiến trình sản xuất Intel 18A, đồng thời là sản phẩm Xeon đầu tiên thương mại hóa công nghệ đóng gói 3D tiên tiến Foveros Direct. Không quá khi nhận xét rằng Clearwater Forest là kỳ quan công nghệ hiện đại, cho thấy sự kỳ công về mặt kỹ thuật của đội ngũ kỹ sư Intel để kết hợp từ tiến trình sản xuất, công nghệ đóng gói tới vi kiến trúc nhân trong cùng 1 sản phẩm.

Intel 18A với RibbonFET và PowerVia

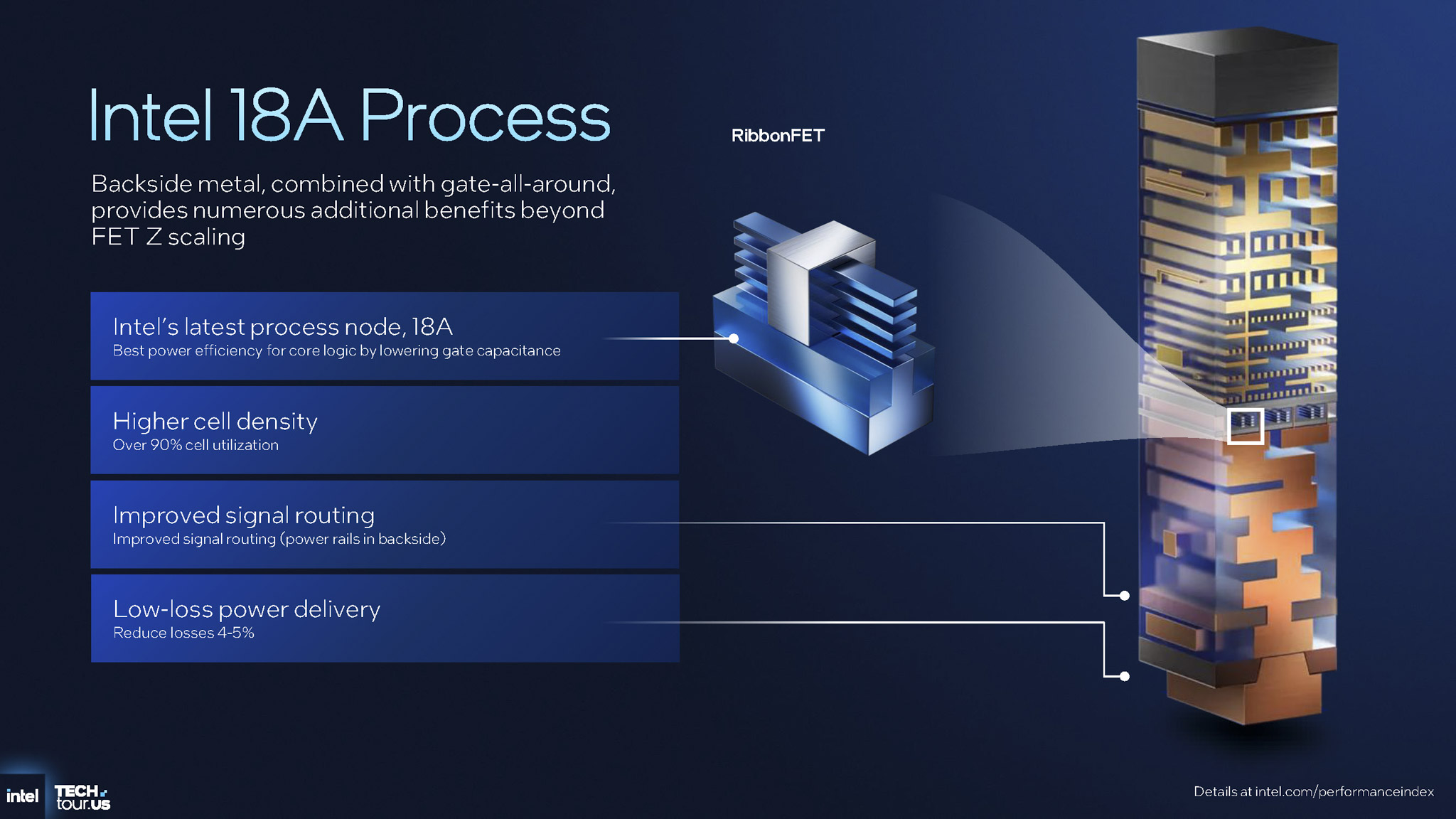

Tiến trình Intel 18A là nền tảng cho những tiến bộ về hiệu năng và hiệu quả năng lượng của Xeon 6+. Intel 18A sở hữu 2 cải tiến đột phá là RibbonFET và PowerVia.

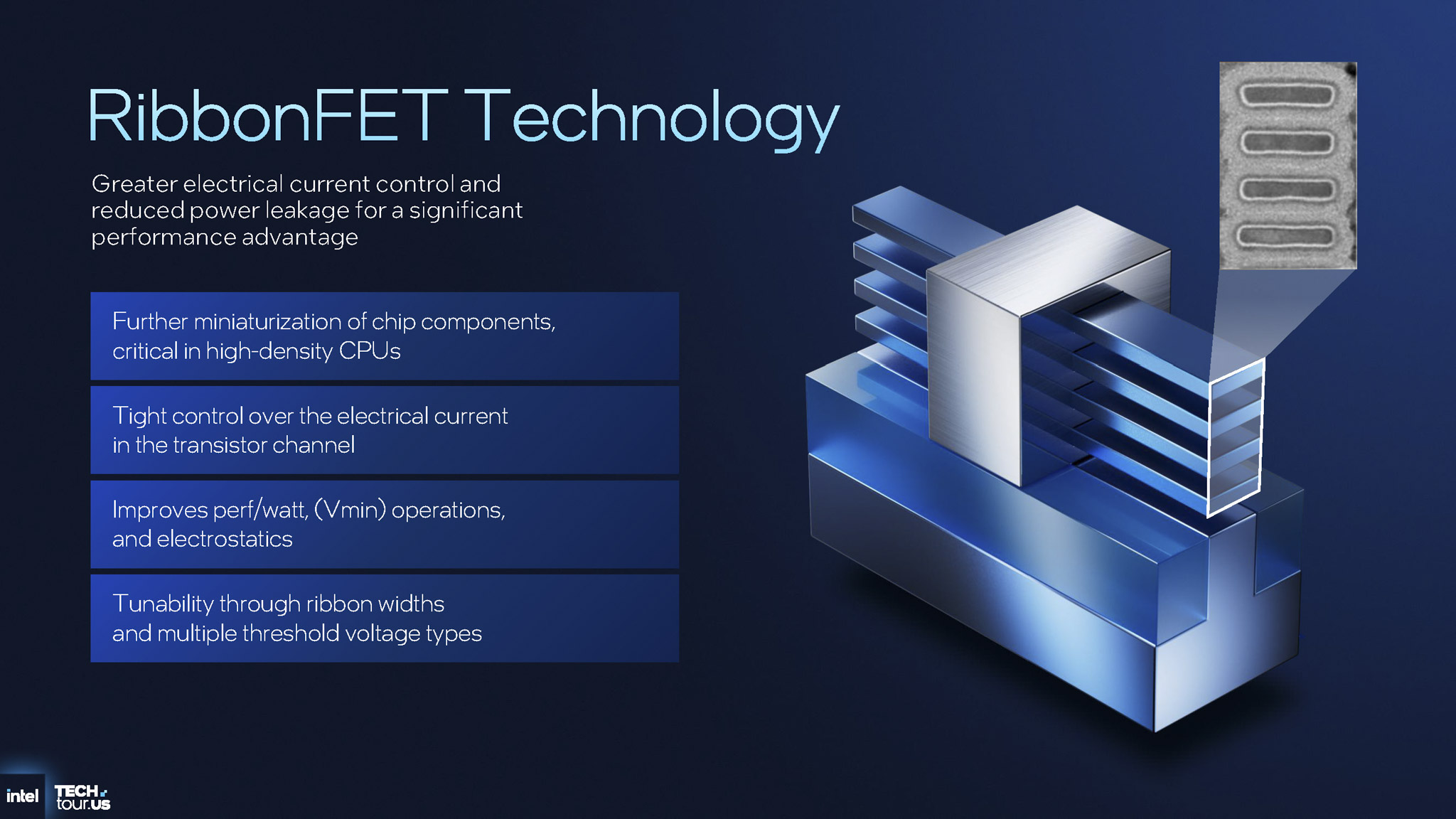

RibbonFET là kiến trúc transistor dạng cổng bao quanh (Gate-All-Around – GAA) của Intel. Khác với kiến trúc FinFET trước đây, cổng (gate) trong RibbonFET bao bọc hoàn toàn các kênh bán dẫn dạng dải băng (ribbon). Cấu trúc này cho phép kiểm soát chặt chẽ dòng điện, giúp tăng dòng điều khiển (drive current) đồng thời giảm đáng kể dòng rò (leakage current). Kết quả là hiệu năng trên mỗi watt cải thiện rõ rệt, cho phép transistor hoạt động ở mức điện áp thấp hơn, góp phần quan trọng vào việc tiết kiệm năng lượng tổng thể của con chip.

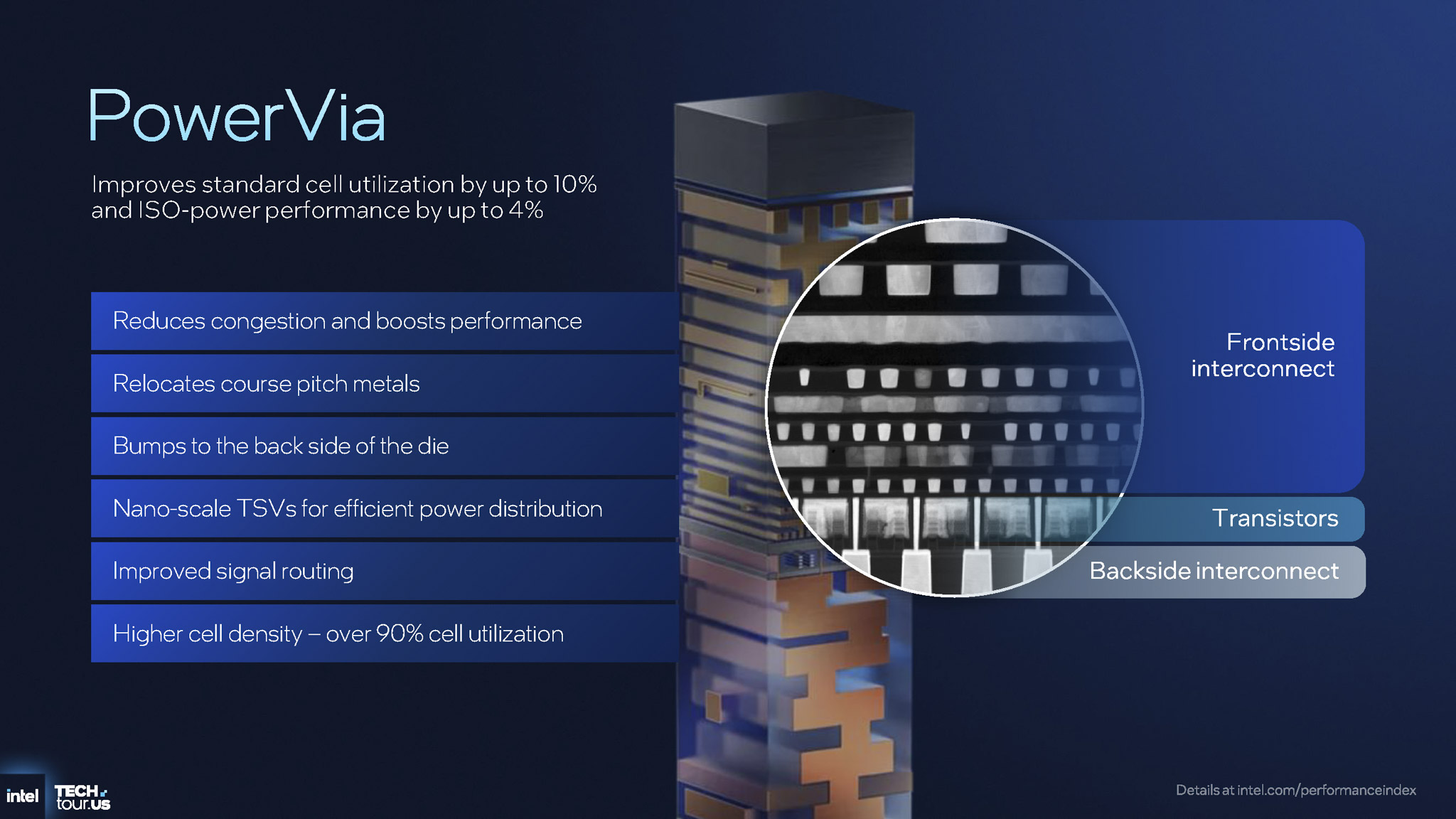

PowerVia là công nghệ cấp nguồn từ mặt sau (backside power delivery) đầu tiên trong ngành. Theo truyền thống, cả đường dẫn tín hiệu và đường cấp nguồn đều được đặt ở mặt trước của wafer, gây ra sự tắc nghẽn và sụt áp (IR drop). PowerVia đã di chuyển toàn bộ lưới điện ra mặt sau của wafer, kết nối trực tiếp với transistor thông qua các đường nối xuyên silicon (Through-Silicon Via – TSV) siêu nhỏ. Việc này giải phóng hoàn toàn các lớp kim loại ở mặt trước cho việc định tuyến tín hiệu, giúp giảm điện trở của lưới điện, giảm tổn thất năng lượng từ 4-5%, cho phép các nhà thiết kế tăng mật độ sắp xếp các cell tiêu chuẩn lên trên 90%. PowerVia là yếu tố then chốt giúp Intel có thể “nhồi nhét” số lượng nhân gấp đôi vào cùng 1 diện tích socket so với thế hệ trước.

Khi Intel triển khai thành công tiến trình 18A lên 1 sản phẩm phức tạp như Clearwater Forest, nó cho thấy Intel đã lấy lại vị thế dẫn đầu về công nghệ. Đối với mô hình kinh doanh IDM 2.0 và chiến lược IFS, việc đưa Intel 18A vào sản xuất hàng loạt với 1 sản phẩm máy chủ cao cấp cũng là màn trình diễn năng lực cho khách hàng tiềm năng của IFS. Nhìn vào Xeon 6+, các khách hàng fabless có thể tin tưởng vào tiến trình và công nghệ của Intel đã sẵn sàng cho những thiết kế phức tạp nhất.

Foveros Direct 3D

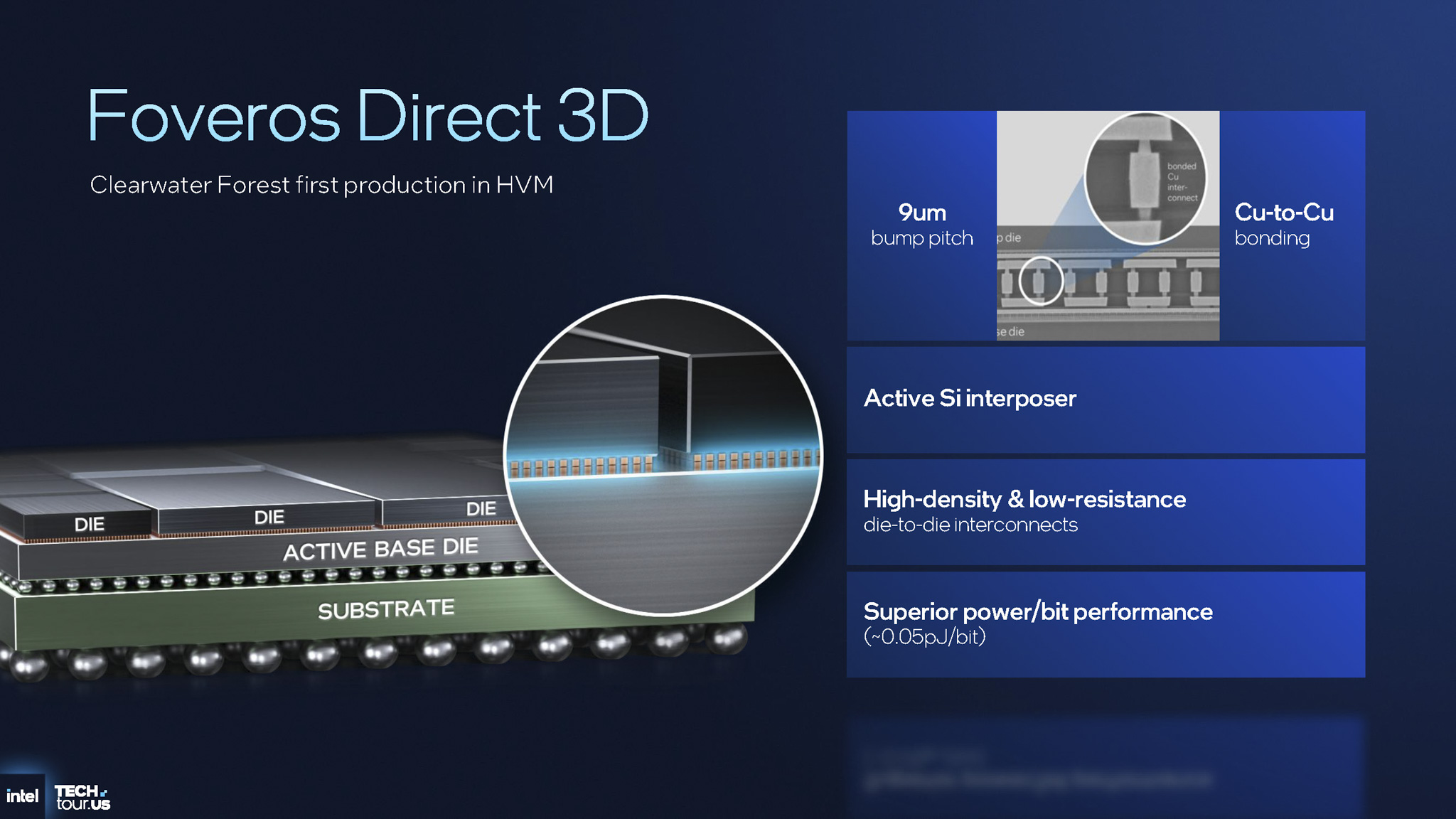

Công nghệ đóng gói Foveros Direct 3D là đỉnh cao của hành trình phân mảnh (disaggregation journey) mà Intel theo đuổi. Intel đã có quá trình tiến hóa rõ ràng từ các thiết kế nguyên khối (monolithic) trên tiến trình Intel 10 nm (Ice Lake), sang kiến trúc 2.5D sử dụng cầu nối EMIB trên tiến trình Intel 7 (Sapphire Rapids). Kế đó là kiến trúc 2.5D với các khối chức năng (tile) riêng biệt sử dụng các tiến trình khác nhau (Xeon 6 Sierra Forest, kết hợp Intel 7 và Intel 3). Clearwater Forest là bước tiến hóa cuối cùng trong hành trình phân mảnh này, kết hợp cả đóng gói 2.5D (EMIB) và 3D (Foveros Direct) với 3 tiến trình sản xuất khác nhau (Intel 18A, Intel 3 và Intel 7) trên cùng 1 đế (package).

Foveros Direct 3D là công nghệ xếp chồng die 3D thế hệ mới của Intel, lần đầu được áp dụng trên dòng Xeon. Nó sử dụng liên kết đồng-với-đồng (Cu-to-Cu) trực tiếp thay vì các mối hàn vi mô (microbumps), cho phép đạt được khoảng cách kết nối (bump pitch) siêu nhỏ chỉ 9 micromet (9 μm). Điều này tạo ra mật độ kết nối cực cao, cho phép băng thông die-to-die khổng lồ với mức tiêu thụ năng lượng gần như bằng không, chỉ khoảng 0.05 picojoules trên mỗi bit (0.05 pJ/bit), hay 50 femtojoules/bit. Mức năng lượng cực thấp này là yếu tố cực kỳ quan trọng, bởi nếu không, việc di chuyển dữ liệu giữa các die xếp chồng sẽ tiêu tốn lượng điện năng đáng kể, làm triệt tiêu lợi ích của việc xếp chồng 3D.

Kiến trúc phân mảnh mang lại cho Intel chiến lược kinh doanh linh hoạt. Bằng cách chia nhỏ SoC thành các “khối LEGO” chức năng (tile), Intel có thể:

- Tối ưu hóa chi phí và hiệu quả: Chỉ sử dụng tiến trình Intel 18A đắt đỏ nhất cho các nhân CPU (Compute Tile), trong khi các khối I/O và Fabric có thể sử dụng các tiến trình đã hoàn thiện, rẻ hơn như Intel 7 và Intel 3.

- Tăng tốc độ ra mắt sản phẩm: Tái sử dụng các tile đã được kiểm chứng, chẳng hạn như I/O Tile từ thế hệ Granite Rapids, giúp giảm đáng kể thời gian và chi phí R&D, đồng thời đảm bảo tính tương thích ngược với nền tảng Birch Stream hiện tại.

- Tạo ra dải sản phẩm đa dạng: Về lý thuyết, Intel có thể linh hoạt kết hợp các loại Compute Tile khác nhau (P-core, E-core, hoặc các tile tăng tốc chuyên dụng) với cùng 1 bộ I/O Tile và Base Tile để nhanh chóng tạo ra các sản phẩm tùy chỉnh, phù hợp cho nhiều phân khúc thị trường khác nhau.

Kiến trúc SoC của Clearwater Forest

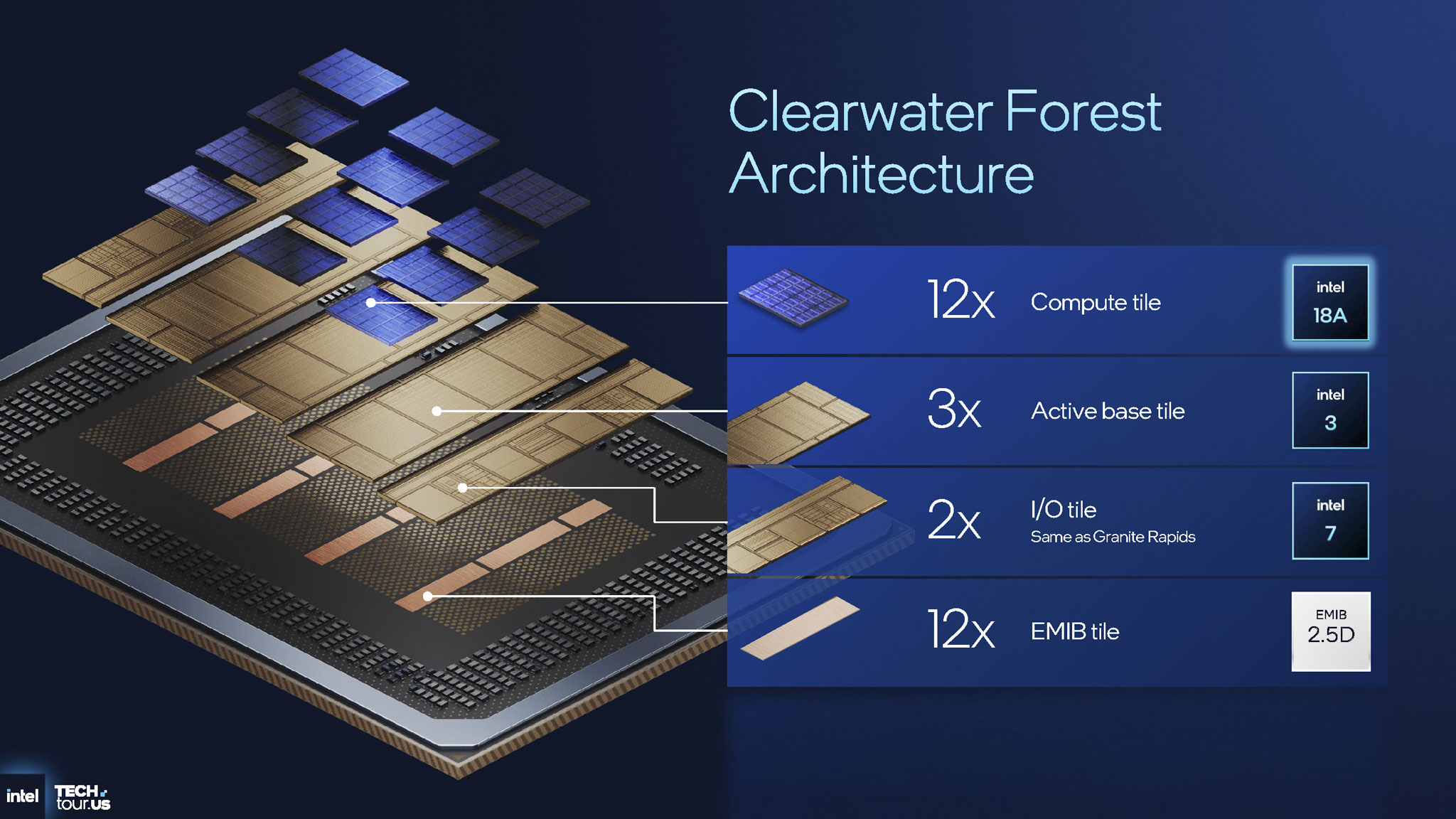

Clearwater Forest cho thấy mức độ phức tạp và tinh vi của công nghệ đóng gói hiện đại. Thay vì 1 die silicon nguyên khối, bộ xử lý Clearwater Forest hoàn chỉnh là hệ thống-trong-một-gói (system-in-package) gồm nhiều chiplet (hay tile) được kết nối với nhau theo cả chiều ngang và chiều dọc. Cấu trúc trên mỗi socket gồm:

- 12 Compute Tile: Chứa các E-core Darkmont, được sản xuất trên tiến trình Intel 18A tiên tiến nhất, cùng với L2 cache. Compute Tile kết nối với Base Tile bằng Foveros Direct 3D.

- 3 Base Tile: Đóng vai trò là nền tảng, chứa bộ đệm LLC, fabric kết nối và bộ điều khiển bộ nhớ, được sản xuất trên tiến trình Intel 3. Base Tile kết nối với Compute Tile bằng Foveros Direct 3D, đồng thời kết nối với các Base Tile khác cũng như I/O Tile bằng EMIB.

- 2 I/O Tile: Xử lý tất cả các giao tiếp ngoại vi (kết nối PCIe, CXL, UPI), sản xuất trên tiến trình Intel 7 và được tái sử dụng từ thế hệ trước. I/O Tile kết nối với Base Tile thông qua EMIB.

Các khối này được lắp ráp theo cấu trúc 2 tầng. Ở tầng dưới (2.5D), 3 Base Tile và 2 I/O Tile đặt cạnh nhau trên đế chip hữu cơ (organic substrate), kết nối thông qua 12 cầu nối EMIB. Ở tầng trên (3D), mỗi Base Tile lại có 4 Compute Tile được xếp chồng trực tiếp lên trên bằng công nghệ Foveros Direct 3D. Cấu trúc này giống như việc xây dựng 1 tòa nhà chọc trời (các lớp 3D) trên 1 khu đô thị được quy hoạch cẩn thận (nền 2.5D), đòi hỏi sự chính xác tuyệt đối trong việc quản lý tín hiệu, cấp nguồn và tản nhiệt.

I/O Tile (Intel 7)

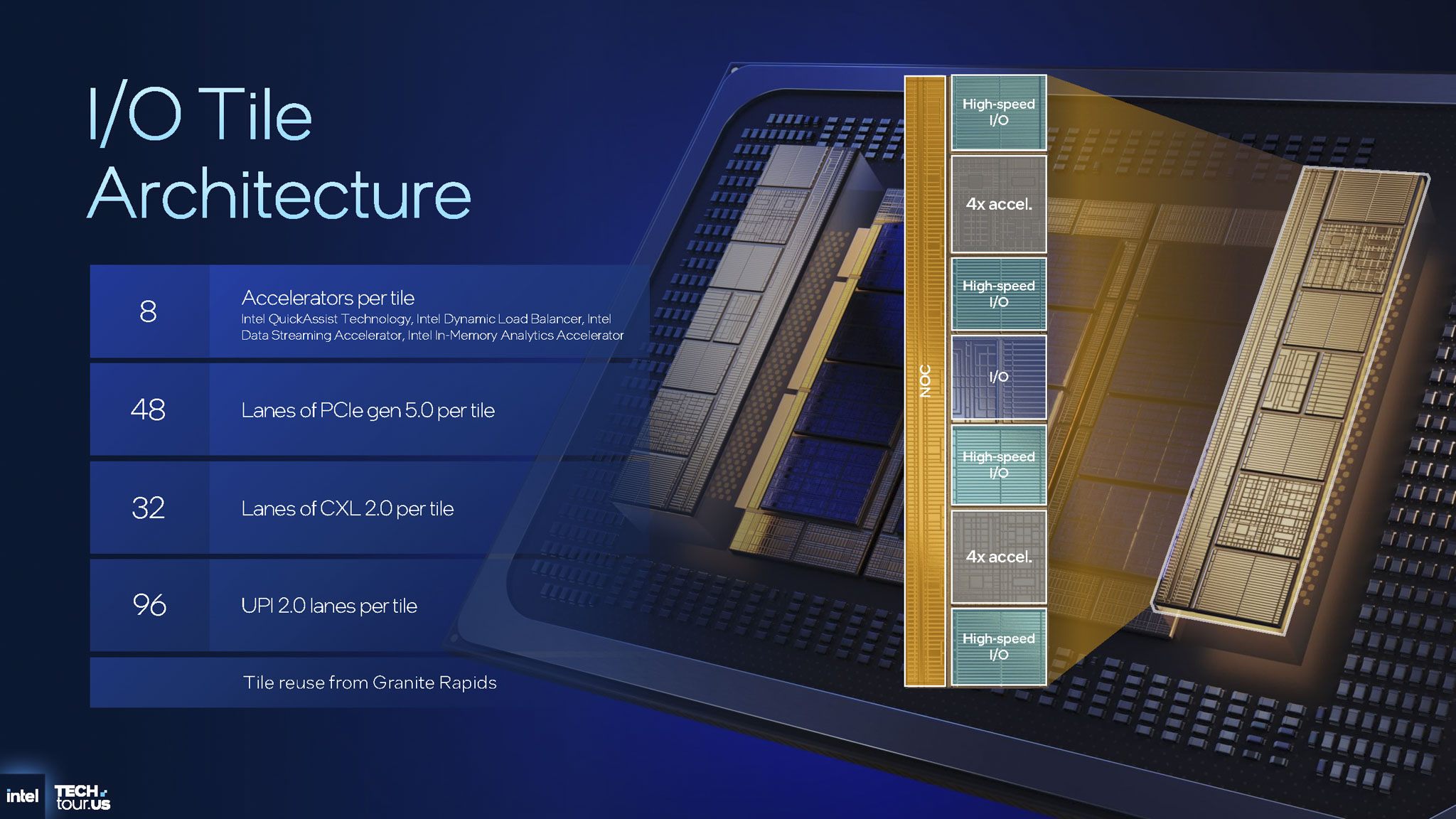

I/O Tile đóng vai trò là cửa ngõ giao tiếp của toàn bộ SoC với thế giới bên ngoài. Intel quyết định tái sử dụng hoàn toàn I/O Tile từ thế hệ Granite Rapids, giúp tiết kiệm chi phí và thời gian R&D. Tái sử dụng I/O Tile còn đảm bảo Clearwater Forest tương thích hoàn toàn với nền tảng Birch Stream đã ra mắt, cho phép các đối tác OEM/ODM nâng cấp lên CPU mới mà không cần thiết kế lại bo mạch chủ.

Mỗi I/O Tile trang bị các giao diện và bộ tăng tốc phần cứng gồm:

- Kết nối ngoại vi: 48 làn PCIe Gen 5.0, trong đó 32 làn có thể hoạt động ở chế độ CXL 2.0 để kết nối với bộ nhớ và các thiết bị tăng tốc thế hệ mới.

- Kết nối đa socket: 96 làn UPI 2.0 (Ultra Path Interconnect) để giao tiếp tốc độ cao giữa các socket trong hệ thống máy chủ nhiều bộ xử lý Xeon 6+.

- Các khối tăng tốc tích hợp: Mỗi tile chứa 8 khối tăng tốc, gồm Intel QuickAssist Technology (QAT) cho mã hóa và nén, Intel Dynamic Load Balancer (DLB) để phân phối tải mạng, Intel Data Streaming Accelerator (DSA) để tối ưu hóa việc di chuyển dữ liệu, Intel In-Memory Analytics Accelerator (IAA) cho các tác vụ cơ sở dữ liệu và phân tích.

Với 2 I/O Tile trên mỗi socket, tổng băng thông kết nối của Clearwater Forest là cực kỳ lớn, đủ sức đáp ứng cho các hệ thống lưu trữ, mạng và AI có nhu cầu cao nhất. Việc tích hợp sẵn các khối tăng tốc nhằm giảm tải các tác vụ cơ sở hạ tầng khỏi các nhân CPU, dành sức mạnh tính toán cho các ứng dụng chính.

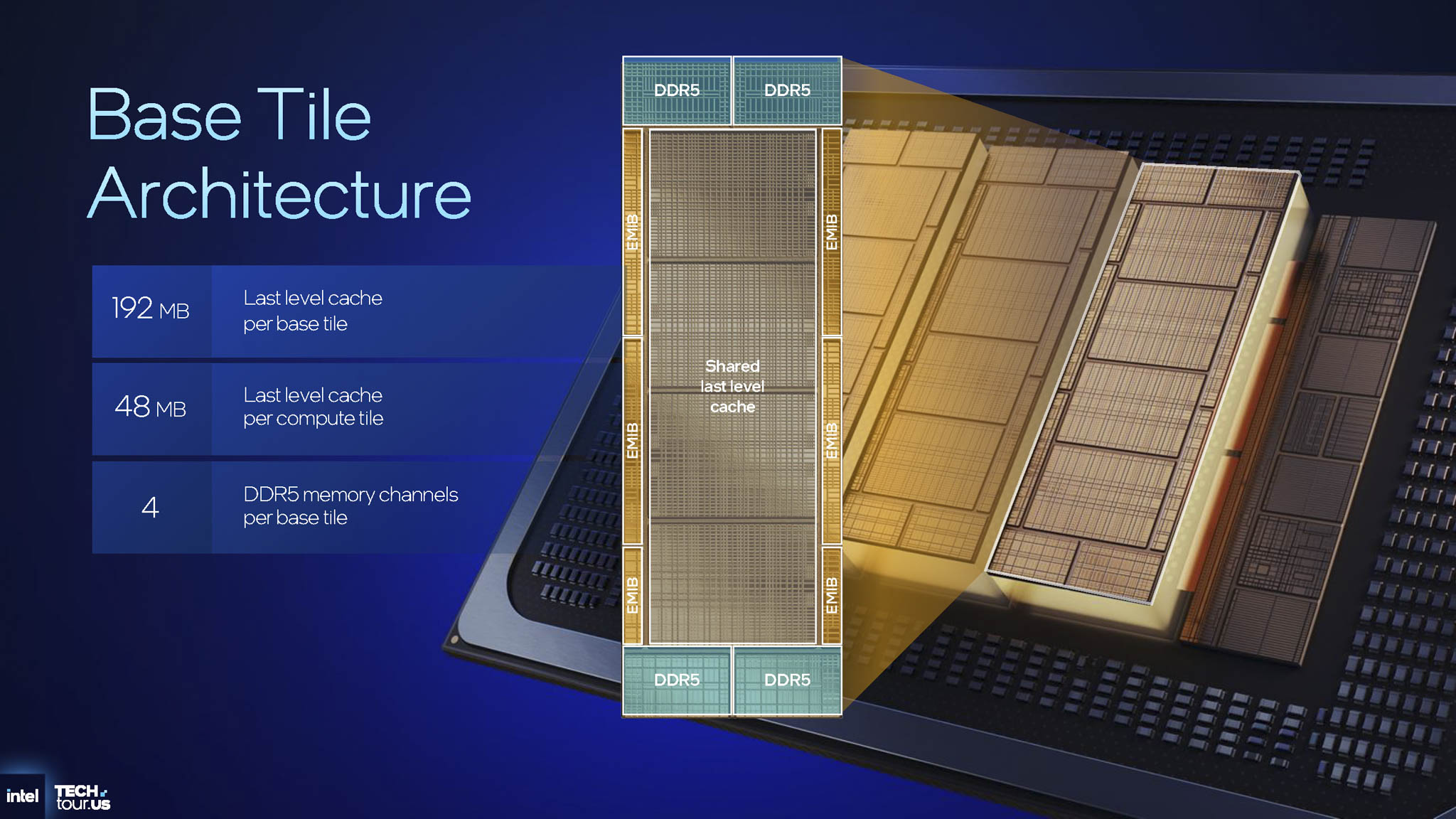

Base Tile (Intel 3)

Base Tile là trung tâm thần kinh của SoC, là nơi hội tụ của mọi luồng dữ liệu. Được sản xuất trên tiến trình Intel 3 đã hoàn thiện và được tối ưu hóa cho mật độ SRAM cao. Mỗi Base Tile đảm nhiệm 2 chức năng:

- Bộ đệm cấp cuối (LLC): Mỗi Base Tile chứa bộ đệm LLC khổng lồ 192 MB. Với 3 Base Tile trong 1 socket, tổng dung lượng LLC lên tới 576 MB, cung cấp vùng đệm dữ liệu cực lớn. LLC lớn giúp giảm độ trễ truy cập bộ nhớ chính và giữ cho các nhân CPU luôn được cung cấp đủ dữ liệu.

- Bộ điều khiển bộ nhớ: Mỗi Base Tile tích hợp bộ điều khiển cho 4 kênh bộ nhớ DDR5. Do đó, toàn bộ socket hỗ trợ 12 kênh DDR5. Đây là nâng cấp đáng kể so với 8 kênh của thế hệ Sierra Forest 6700E, cung cấp băng thông bộ nhớ cần thiết để phục vụ cho 288 nhân.

Ngoài ra, Base Tile còn là nơi chứa fabric kết nối (coherent fabric), đảm bảo tính nhất quán dữ liệu giữa bộ đệm của tất cả các nhân và LLC.

Compute Tile (Intel 18A)

Compute Tile là nơi chứa “bộ não” của bộ xử lý Clearwater Forest – các nhân E-core Darkmont. Việc chia nhỏ 288 nhân thành 12 Compute Tile riêng biệt, mỗi tile chỉ chứa 24 nhân, là chiến lược quan trọng để đạt được tỷ lệ sản phẩm thành công (yield) cao trên tiến trình 18A còn non trẻ. Nếu 1 Compute Tile bị lỗi trong quá trình sản xuất, Intel có thể dễ dàng vô hiệu hóa nó và bán ra 1 SKU với số nhân ít hơn, thay vì phải loại bỏ toàn bộ 1 die lớn và đắt tiền.

Cấu trúc bên trong mỗi Compute Tile gồm có 6 module. Từng module chứa 4 nhân Darkmont cùng chia sẻ bộ đệm L2 hợp nhất dung lượng 4 MB. Cấu trúc module 4 nhân chia sẻ L2 cache giúp cân bằng giữa độ trễ truy cập L2 thấp (do các nhân ở gần nhau) và tiết kiệm diện tích die. Tổng cộng, với 12 Compute Tile, 72 module và 288 nhân, Clearwater Forest mang lại một mật độ tính toán cực cao.

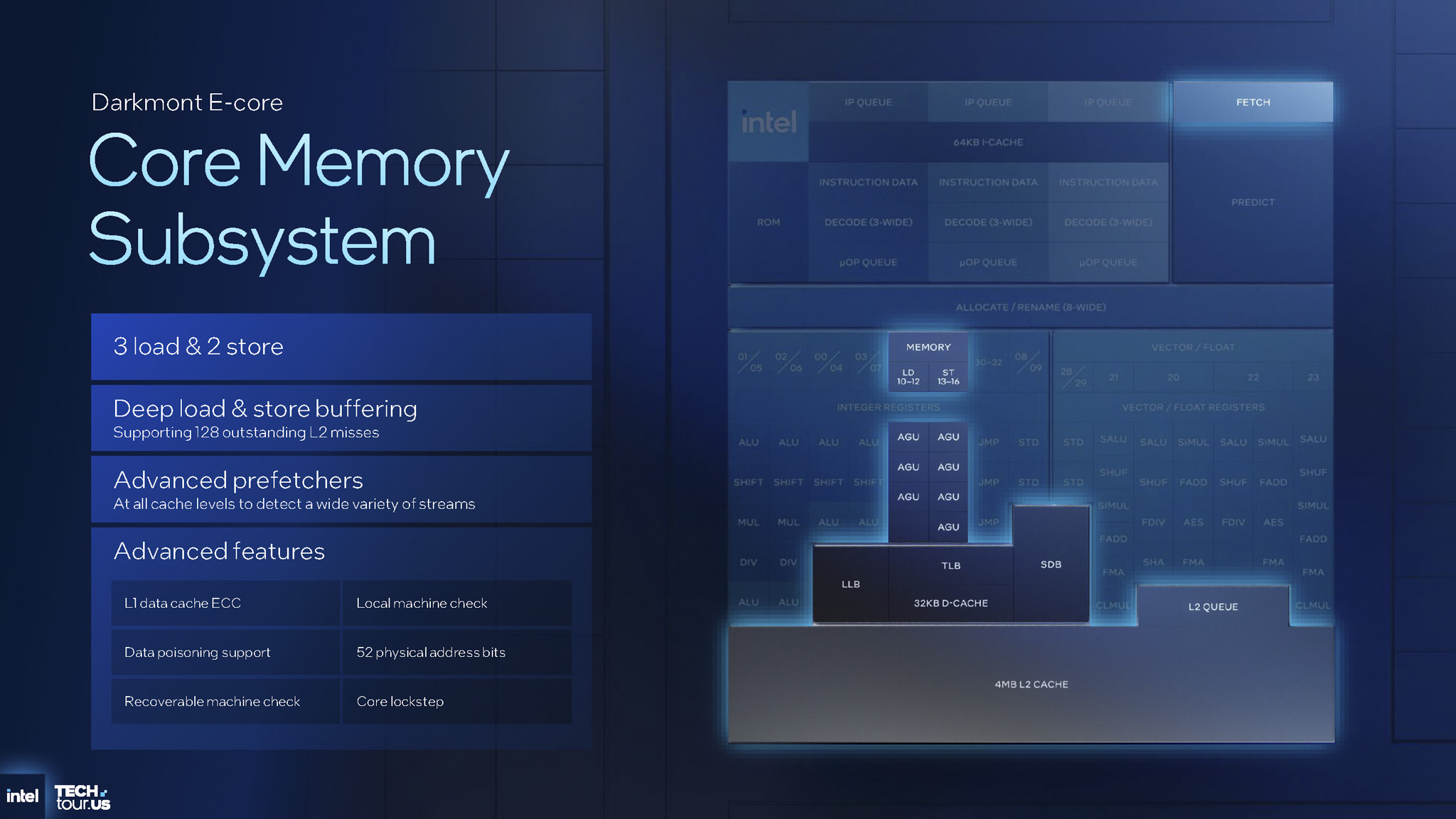

Vi kiến trúc Darkmont E-core

“Quái thú tí hon”

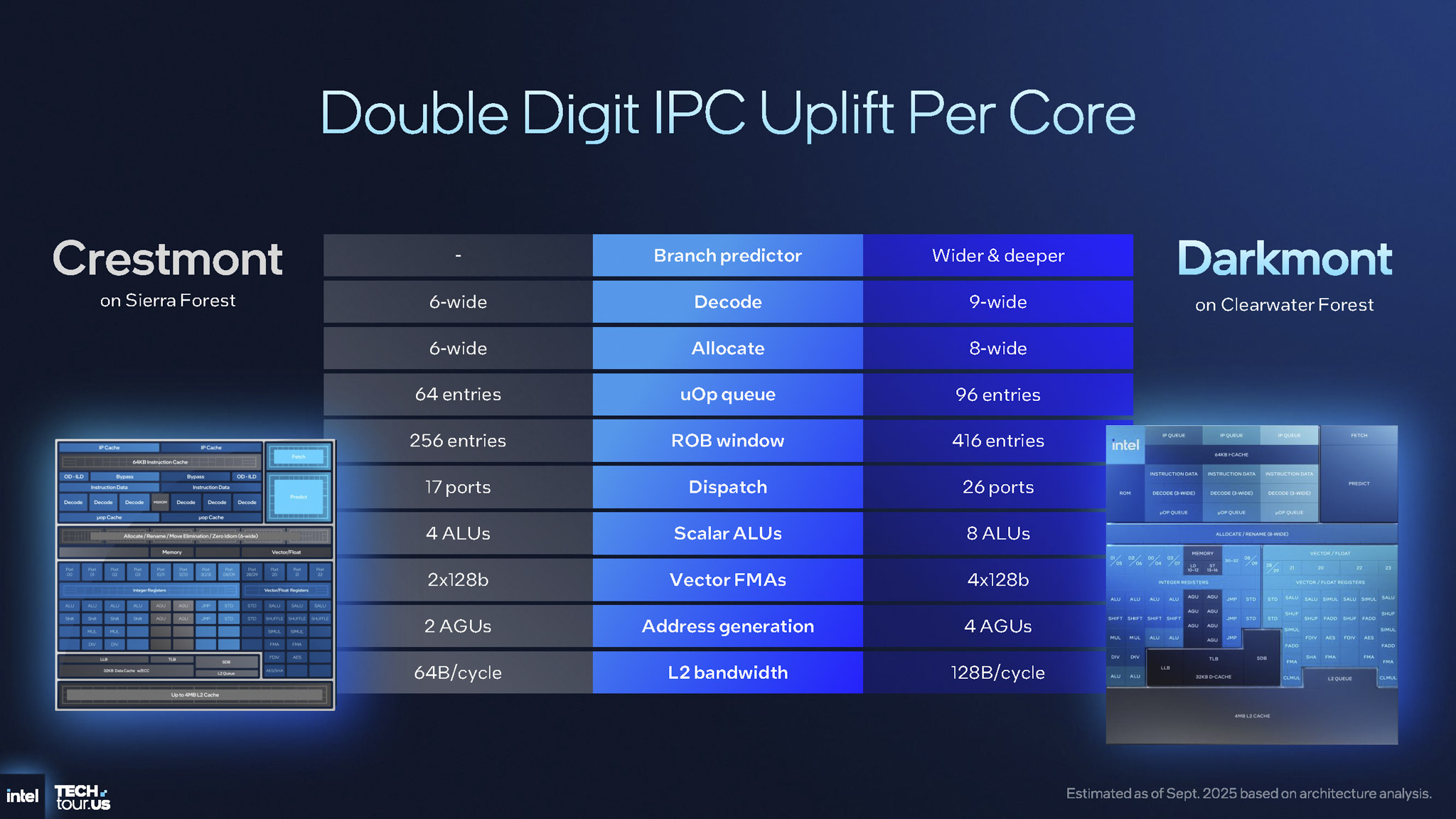

Nếu Clearwater Forest là bước nhảy vọt về kiến trúc hệ thống, thì vi kiến trúc E-core Darkmont chính là nguồn gốc sức mạnh cho bước nhảy đó. Được Stephen Robinson, Intel Fellow và kiến trúc sư trưởng cho các nhân x86, mô tả là một “quái thú tí hon” (tiny beast), Darkmont xóa bỏ hoàn toàn định kiến về E-core là những nhân “yếu” chỉ dành cho các tác vụ nền.

So với Crestmont trên Sierra Forest, Darkmont là sự lột xác hoàn toàn mới. Darkmont là vi kiến trúc có độ rộng thực thi (execution width) 8-wide, được cung cấp bởi một front-end 9-wide, đồng thời được hỗ trợ bởi engine thực thi ngoài thứ tự (out-of-order engine) khổng lồ với cửa sổ lên tới 416 entry và 26 cổng thực thi (execution port). Những con số này không chỉ vượt xa Crestmont mà còn tiệm cận với các P-core hiệu năng cao thế hệ trước như Golden Cove (vốn có cửa sổ 512 entry). Điều này cho thấy Darkmont được thiết kế để khai thác tối đa mức độ song song ở cấp độ lệnh (Instruction-Level Parallelism – ILP), có khả năng xử lý hiệu quả các mã máy chủ phức tạp với code footprint lớn.

| Thành phần vi kiến trúc | Crestmont | Darkmont | Mức tăng/Cải tiến |

|---|---|---|---|

| Front-End | |||

| Độ rộng Decode | 6-wide (2×3) | 9-wide (3×3) | +50% băng thông |

| Hàng đợi uop | 64 entry | 96 entry | +50% dung lượng |

| Out-of-Order Engine | |||

| Độ rộng Allocate | 6-wide | 8-wide | +33% |

| Độ rộng Retire | N/A (thấp hơn 16) | 16-wide | Tăng đáng kể |

| ROB window | 256 entry | 416 entry | +62.5% |

| Execution Engine | |||

| Số cổng thực thi | 17 | 26 | +53% |

| ALU số nguyên | 4 | 8 | 2x |

| Đơn vị FMA Vector | 2×128-bit | 4×128-bit | 2x thông lượng |

| AGU (Address Generation) | 2 | 4 | 2x |

| Memory Subsystem | |||

| Băng thông L2 | 64B/chu kỳ | 128B/chu kỳ | 2x |

Front-End

Để cung cấp đủ lệnh cho bộ máy thực thi khổng lồ, Darkmont trang bị front-end cực kỳ mạnh mẽ. Front-end mới sở hữu bộ đệm lệnh (I-Cache) dung lượng lớn 64 KB và bộ dự đoán nhánh (Branch Predictor) nâng cấp, tăng 30% dung lượng từ 6000 lên 8000 mục tiêu (target). Việc cải thiện khả năng dự đoán nhánh là cực kỳ quan trọng đối với các tải công việc máy chủ, vốn có nhiều nhánh và khó dự đoán hơn.

Điểm độc đáo của Darkmont (và cả Crestmont) là kiến trúc front-end phân cụm (clustered). Thay vì 1 bộ giải mã (decoder) 9-wide nguyên khối, Darkmont sử dụng 3 cụm giải mã 3-wide độc lập, hoạt động ngoài thứ tự (out-of-order) với nhau. Mỗi khi dự đoán một nhánh được thực hiện (taken branch), một cụm giải mã mới sẽ được kích hoạt để bắt đầu giải mã các lệnh từ địa chỉ đích mới. Miễn là bộ dự đoán nhánh có thể đi trước, cả 3 cụm có thể hoạt động song song, cung cấp băng thông giải mã tổng cộng là 9-wide. Từ các triển khai thực tế của Sierra Forest, Intel đã bổ sung các cơ chế “heuristic” để giảm bớt suy đoán quá mức (over-speculation) – tối ưu hóa quan trọng dành riêng cho môi trường máy chủ.

Out-of-Order Engine và Execution Engine

Sau khi được giải mã, các vi lệnh (micro-ops) được đưa vào out-of-order engine. Darkmont có thể cấp phát (allocate) 8 vi lệnh mỗi chu kỳ vào cửa sổ ROB 416 entry và hoàn tất (retire) tới 16 vi lệnh mỗi chu kỳ. Việc tăng gấp đôi độ rộng retirement so với các thiết kế trước đây giúp giải phóng tài nguyên trong máy nhanh hơn đáng kể, đặc biệt quan trọng để xử lý nhanh các lệnh store vốn không thể thực thi suy đoán. Từ cửa sổ ROB, các vi lệnh được gửi đến 1 trong 26 cổng thực thi – con số khổng lồ cho thấy khả năng xử lý song song của Darkmont. Các cổng thực thi này gồm:

- 8 đơn vị số học và logic (ALU) số nguyên.

- 3 cổng tải (load) và 2 cổng lưu trữ (store).

- Thông lượng tính toán vector (FMA) và AI (VNNI) tăng gấp đôi so với Crestmont.

Sự gia tăng về tài nguyên thực thi, đặc biệt là thông lượng vector/AI, cho thấy Intel đang định vị E-core không chỉ cho các tác vụ số nguyên truyền thống mà còn cho các tải công việc đa phương tiện và suy luận AI (AI inference) ngày càng phổ biến.

Memory Subsystem và tính năng RAS

Để “nuôi” cỗ máy xử lý 288 nhân, hệ thống bộ nhớ phụ trợ phải cực kỳ mạnh mẽ. Darkmont có thể duy trì băng thông tải dữ liệu từ L1 cache lên tới 48 bytes mỗi chu kỳ (3 loads × 16 bytes/load). Băng thông giữa L1 và L2 cache cũng tăng gấp đôi so với Crestmont, đạt 128 bytes/chu kỳ. Ngoài ra, các cơ chế tìm nạp trước (prefetcher) ở mọi cấp độ cache đều được cải tiến. Bên cạnh đó, prefetcher cũng có khả năng nhận “telemetry” từ fabric của SoC để tự động điều chỉnh mức độ hoạt động, tránh làm nghẽn băng thông hệ thống khi không cần thiết.

Nhưng, điểm nhấn thực sự của Darkmont nằm ở các tính năng Độ tin cậy, Tính sẵn sàng và Khả năng phục vụ (Reliability, Availability and Serviceability – RAS) cấp doanh nghiệp, vốn thường chỉ xuất hiện trên các P-core cao cấp.

- L1 Data Cache ECC: Bộ đệm dữ liệu L1 được trang bị mã sửa lỗi (Error Correcting Code), có khả năng sửa các lỗi bit đơn và phát hiện các lỗi bit kép, đảm bảo tính toàn vẹn của dữ liệu ngay từ cấp độ gần nhất với nhân xử lý.

- Data Poisoning & Recoverable Machine Check: Khi một lỗi không thể sửa được xảy ra, hệ thống có khả năng “đánh dấu độc” (poisoning) dữ liệu bị lỗi để ngăn nó lan truyền và gây hỏng hóc các phần khác của hệ thống. Các cơ chế kiểm tra máy có thể phục hồi (Recoverable Machine Check) cho phép phần mềm (hệ điều hành hoặc hypervisor) xử lý lỗi chính xác hơn, có thể chỉ cần chấm dứt ứng dụng hoặc máy ảo thay vì làm sập toàn bộ hệ thống.

- Core Lockstep: Đây là tính năng RAS cao cấp nhất được tích hợp. Lockstep cho phép 2 nhân trong cùng 1 module hoạt động đồng bộ, thực thi cùng 1 luồng lệnh. Ở mỗi chu kỳ, kết quả của chúng được so sánh. Nếu có bất kỳ sự khác biệt nào, dù là nhỏ nhất (do 1 lỗi phần cứng tạm thời), hệ thống sẽ ngay lập tức phát hiện và báo cáo lỗi.

Việc tích hợp tính năng cấp mainframe như Core Lockstep vào E-core là điểm cực kỳ quan trọng. Điều này cho thấy Intel không chỉ nhắm đến thị trường đám mây nói chung mà còn nhắm đến các phân khúc yêu cầu độ tin cậy cực cao như mạng lõi 5G (5G Core network), hệ thống giao dịch tài chính và các ứng dụng khoa học, nơi mà 1 lỗi dữ liệu không bị phát hiện (silent data error) có thể gây ra những hậu quả thảm khốc. Core Lockstep là một lợi thế cạnh tranh khác biệt mà các đối thủ sẽ khó có thể sao chép trong ngắn hạn, giúp Intel củng cố vị thế trong các thị trường cốt lõi.

Hiệu năng, hiệu quả và phần mềm

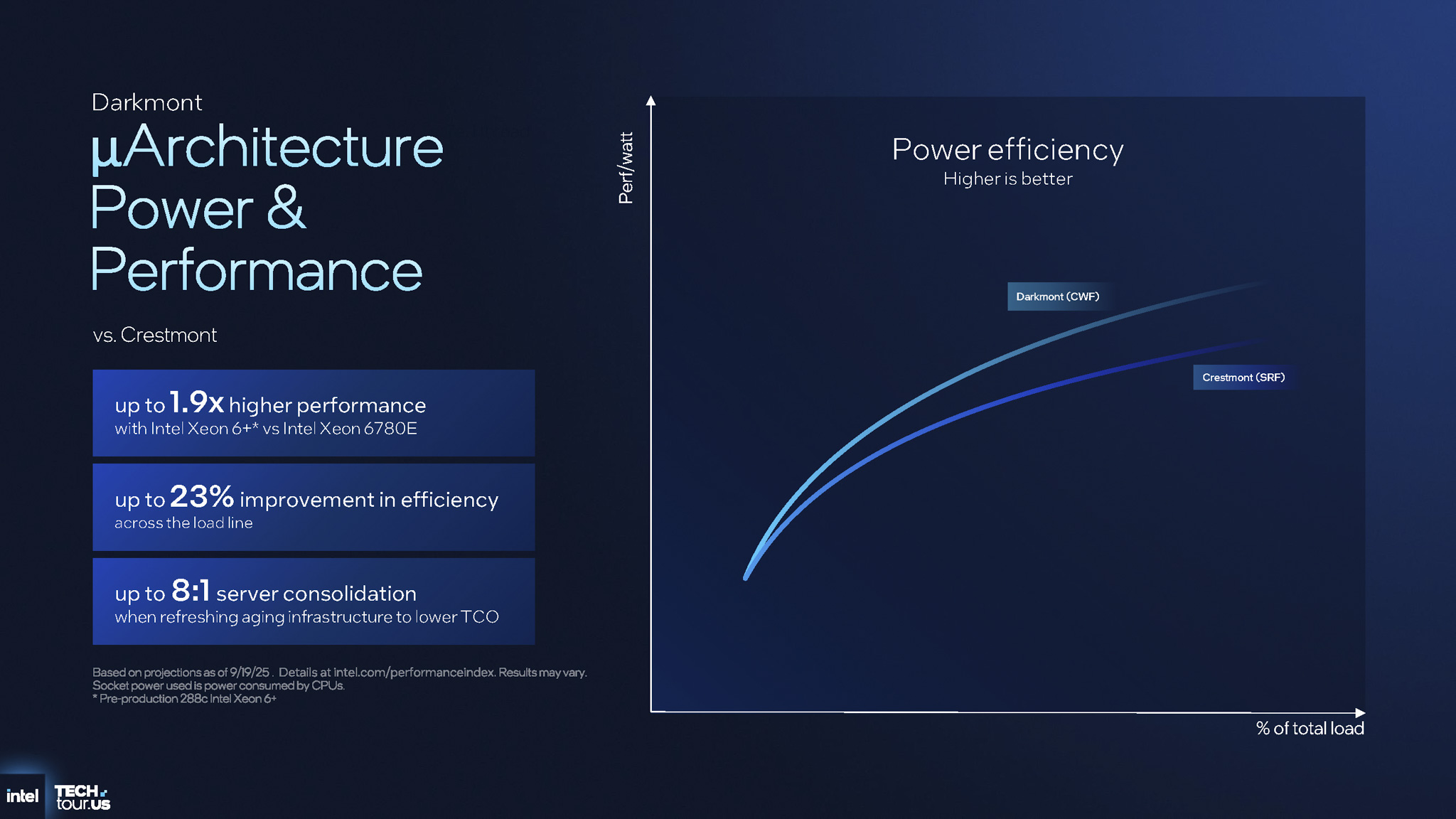

Hiệu năng và hiệu quả năng lượng

Intel trình bày các số liệu hiệu năng ấn tượng cho Xeon 6+ (Clearwater Forest), cho thấy những bước tiến vượt bậc so với các thế hệ trước. So với Xeon 6 6780E (144-core Sierra Forest), Clearwater Forest mang lại hiệu năng cao hơn tới 1.9 lần. Mức tăng này là kết quả của các cải tiến kiến trúc đồng bộ: 17% tăng trưởng IPC (Instructions Per Cycle) trên mỗi nhân, dung lượng LLC lớn hơn 5 lần (576 MB so với 108 MB), tăng 50% số kênh bộ nhớ (12 so với 8) và tốc độ bộ nhớ nhanh hơn 20% (8000 MT/s so với 6400 MT/s).

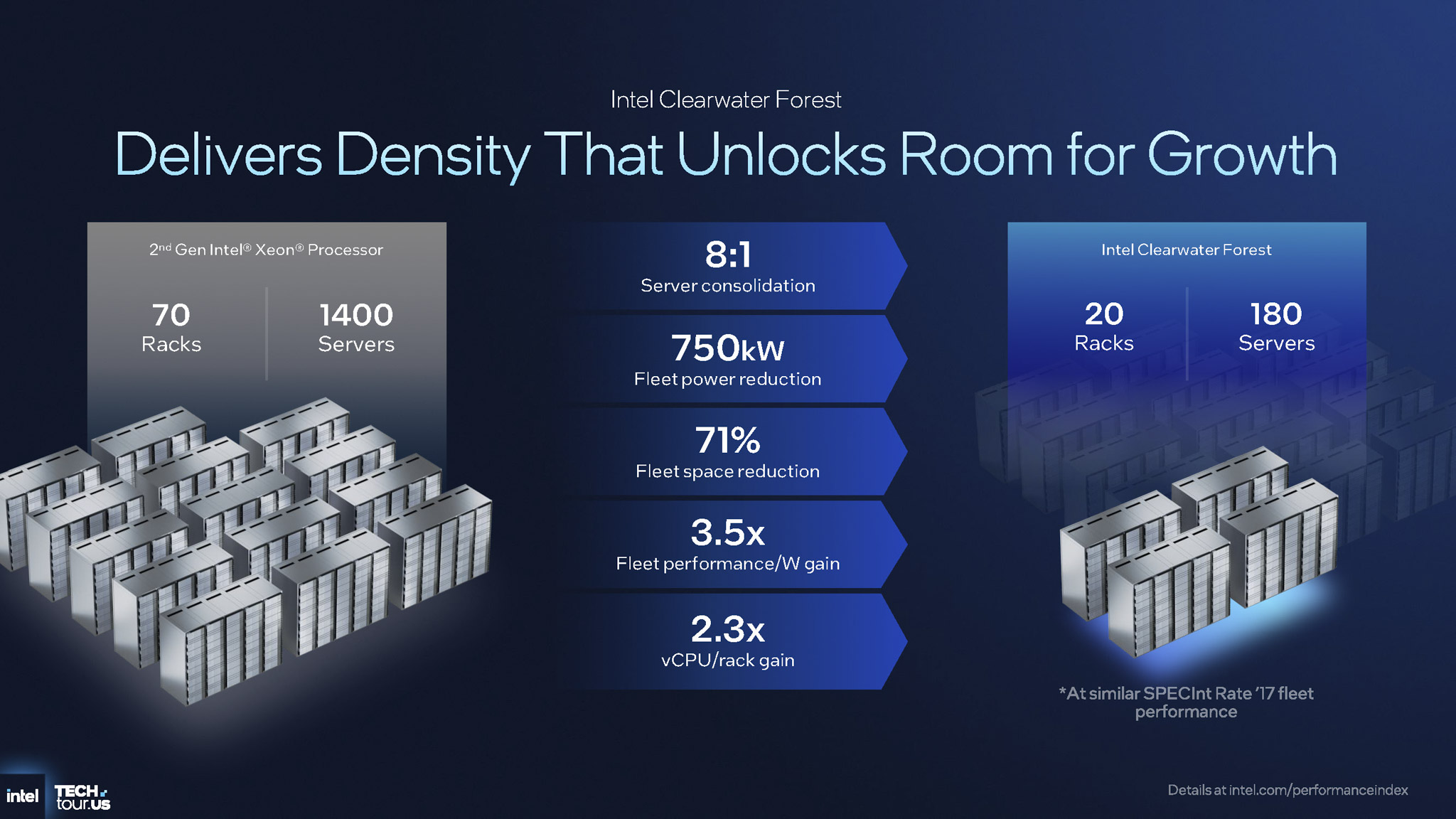

Nền tảng mới cho thấy sự cải thiện hiệu quả năng lượng tới 23% trên toàn bộ dải tải (load line), từ trạng thái nghỉ đến tải tối đa. Đối với các trung tâm dữ liệu đang xem xét nâng cấp từ hạ tầng 5 năm tuổi (Xeon thế hệ 2), Clearwater Forest cung cấp giá trị hấp dẫn với khả năng hợp nhất máy chủ lên tới tỷ lệ 8:1. Điều này có thể giúp giảm tới 750 kW công suất tiêu thụ của 1 cụm máy chủ, đồng thời giảm 71% diện tích sàn cần thiết, trong khi tăng gấp 3.5 lần hiệu năng trên mỗi watt.

Nếu chỉ đơn thuần nhân đôi số nhân từ 144 lên 288, hiệu năng lý thuyết sẽ tăng 2 lần. Việc đạt được mức tăng gần như tuyến tính (1.9x) cho thấy Intel đã giải quyết thành công các nút thắt cổ chai tiềm ẩn. Bằng cách tăng cường đáng kể băng thông bộ nhớ, dung lượng cache và hiệu năng IPC của từng nhân, Intel đảm bảo rằng 288 nhân xử lý không bị “đói” dữ liệu, cho phép chúng phát huy hết tiềm năng.

Tối ưu cho Cloud-Native và Telco

Intel định vị rõ ràng Xeon 6+ là nền tảng lý tưởng cho các hoạt động cloud-native thế hệ mới và mạng lõi 5G (5G Core) cho ngành viễn thông. Các tải công việc này có những đặc điểm chung: chúng được xây dựng trên kiến trúc vi dịch vụ (microservices), có khả năng mở rộng theo chiều ngang cao, cực kỳ nhạy cảm với tổng chi phí sở hữu (TCO), đặc biệt là chi phí điện năng và không gian vật lý.

Clearwater Forest đáp ứng hoàn hảo các yêu cầu này. Với mật độ nhân cực cao (lên đến 576 nhân trong máy chủ 2-socket), hiệu quả năng lượng vượt trội nhờ tiến trình 18A và vi kiến trúc Darkmont, cùng với băng thông bộ nhớ khổng lồ, nền tảng này cho phép các nhà cung cấp dịch vụ đám mây và viễn thông phục vụ nhiều người dùng hoặc kết nối hơn trên mỗi rack. Điều này trực tiếp cải thiện hiệu quả hoạt động và lợi nhuận.

Hệ sinh thái phần mềm

Như thường lệ, phần cứng mạnh mẽ chỉ là một nửa của câu chuyện. Lợi thế cạnh tranh của Intel vẫn nằm ở hệ sinh thái phần mềm x86 rộng lớn và trưởng thành. Các nhà phát triển có thể tận dụng các công cụ và thư viện được tối ưu hóa cao của Intel để khai thác tối đa sức mạnh của phần cứng mới mà không cần viết lại mã ở mức độ thấp.

Các thư viện như Intel oneAPI Deep Neural Network Library (oneDNN) được cập nhật liên tục để hỗ trợ các tập lệnh mới, giúp tăng tốc các mô hình AI và học sâu. Các trình biên dịch của Intel cũng được tối ưu hóa để tự động vector hóa mã nguồn, tận dụng các đơn vị xử lý vector mạnh mẽ trong nhân Darkmont.

Ngoài ra, Intel còn giới thiệu các công cụ quản lý năng lượng tiên tiến như Intel Application Energy Telemetry (Intel AET). Công cụ này cung cấp khả năng theo dõi và phân tích việc sử dụng năng lượng ở cấp độ ứng dụng, cho phép các nhà quản trị trung tâm dữ liệu đưa ra các quyết định tối ưu hóa thông minh để giảm chi phí vận hành. Công cụ như AET ngày càng trở nên quan trọng trong bối cảnh chi phí điện năng không ngừng tăng cao.

| Thông số kỹ thuật | |

|---|---|

| Nền tảng | |

| Sockets | 1S – 2S (Tương thích Xeon 6900P) |

| Max TDP | 300W đến 500W mỗi CPU |

| Compute & Memory | |

| Số nhân | Lên đến 288 E-core (Darkmont) |

| L2 Cache | Lên đến 288 MB (4 MB mỗi cụm 4 nhân) |

| Last Level Cache | 576 MB |

| Bộ nhớ | 12 kênh DDR5, lên đến 8000 MT/s |

| Kết nối | |

| Intel UPI | Lên đến 6 liên kết UPI 2.0 (lên đến 24 GT/s mỗi lane) |

| PCI Express | Lên đến 96 làn PCIe 5.0 (x16, x8, x4, x2) |

| Compute Express Link | Lên đến 64 làn CXL 2.0 |

| Tăng tốc & Bảo mật | |

| Tăng tốc tích hợp | Lên đến 16 khối (4x QAT, 4x DLB, 4x DSA, 4x IAA) |

| Tập lệnh AI | Intel Advanced Vector Extensions 2 (VNNI/INT8) |

| Bảo mật | Intel SGX, Intel TDX |

| Quản lý năng lượng | Intel AET, Intel Turbo Rate Limiter |

Kết luận

Bằng cách kết hợp tiến trình Intel 18A tiên tiến, công nghệ đóng gói Foveros Direct 3D đột phá và vi kiến trúc E-core Darkmont mạnh mẽ, Clearwater Forest đã thiết lập tiêu chuẩn mới về mật độ tính toán và hiệu quả năng lượng. Việc tích hợp các tính năng RAS cấp doanh nghiệp như Core Lockstep vào E-core cũng cho thấy một chiến lược bảo vệ các thị trường có giá trị cao, tạo ra một rào cản cạnh tranh khác biệt.

Với Clearwater Forest, Intel vừa đưa ra câu trả lời thuyết phục cho các đối thủ trong phân khúc điện toán hiệu quả cao, vừa trình diễn ấn tượng năng lực của mô hình IDM 2.0. Thành công của Xeon 6+ không chỉ ảnh hưởng tích cực cho tương lai của mảng kinh doanh trung tâm dữ liệu, mà còn cho cả mảng gia công bán dẫn của Intel trong những năm tới.